やーやーやー。

ハードウェアをScalaで書ける組み込み言語、Chisel3の入門インストール講座です。

というわけで、面倒でもまずは開発環境を準備するところから始めよう。

ごらんの番組は以下の内容でお送りいたします。

- Chisel開発に必要な物

- JDKのインストール

- Windows上で開発する人

- Linux上で開発する人

- IntelliJ IDEAをインストールする

- Windowsの人

- Linux(Ubuntu)の人

- IntelliJ IDEAの初期設定(Windows、Linux共通)

- プロキシ環境下:プロキシの設定

- プロキシ環境下:プロキシが認証局証明書を上書きする場合

- プロキシ環境下:Scalaプラグインを入れる

- IntelliJ IDEAでChiselを動かしてみる

- おわりに

- 旧情報(Oracle JDKのインストール)

Chisel開発に必要な物

以下の物が揃っていれば、すぐに開発を開始出来ます。

JDKとか、Javaとか、IntelliJ IDEAとか見たこともない謎の横文字が並んでしまって大変申し訳ない。我慢してインストールに付き合ってください。

Verilogを開発するOSはLinuxである可能性も高いから、WindowsとLinux(Ubuntu)で解説します。OSが分からない人は、ExcelがあるのがWindowsで、Excelが無いか、なんかパチモンっぽいのが動くのがLinuxです。

JDKのインストール

JDKというのは、Chiselを動かすのに必要なソフトです。

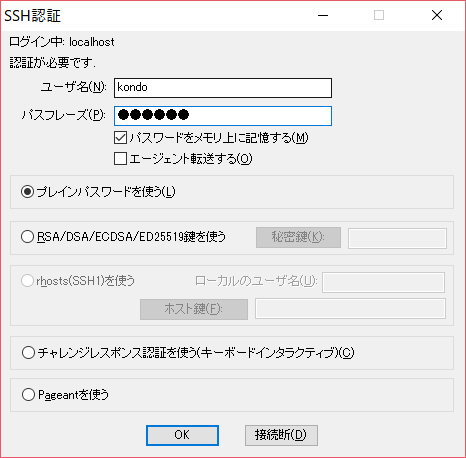

Windows上で開発する人

2019年からOracleのJDKは有償化されます。それに伴い、現在JDKは移行先の混迷期にあります。一応OpenJDKベースで書き直しましたが、

信用はしないで下さい。

無償のJDKとしては、OpenJDK以外にも、Adopt OpenJDKやAmazonのCorrettoがあります。

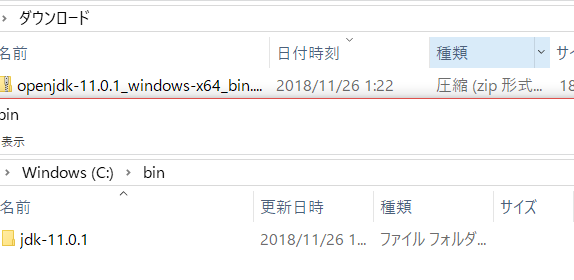

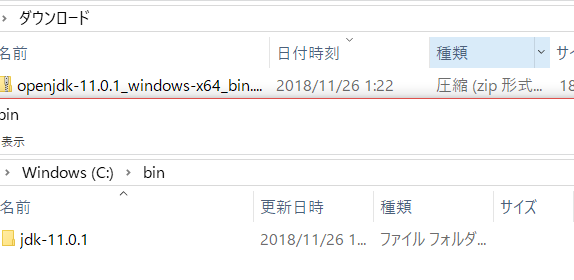

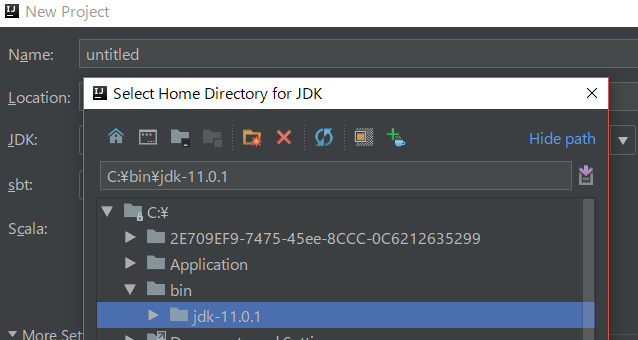

OpenJDKをJDK Builds from Oracleからダウンロードし、任意の場所に展開して下さい。今回は、JDK11というバージョンのWindows版をC:\bin\jdk-11.0.1に展開しました。

画像は2018年11月現在のキャプチャであり、今現在とは必ず違うので、臨機応変に対応して下さい。

JDK11のリンクを押すと、次の様な画面になります。

Windows用をダウンロード(32bitはありません)し、適当な場所に展開します

Linux上で開発する人

Linuxの人用です。Windowsの人は飛ばしてください。

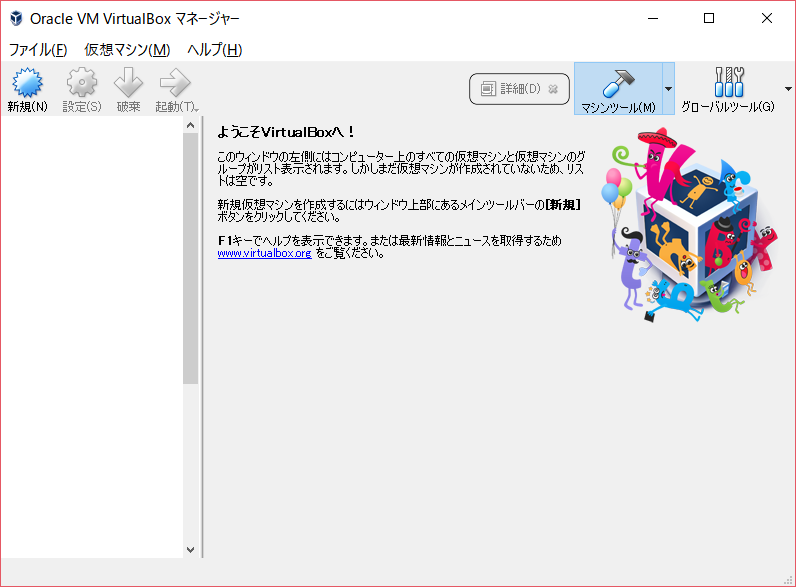

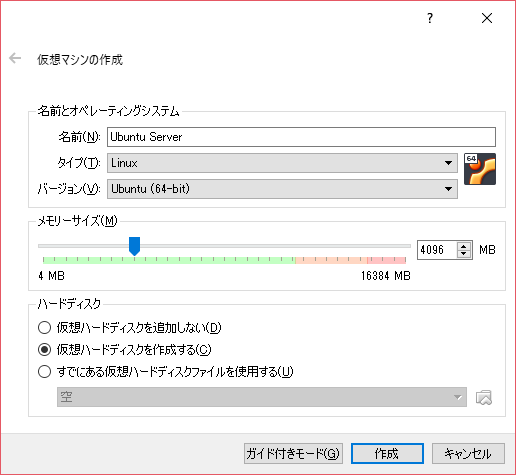

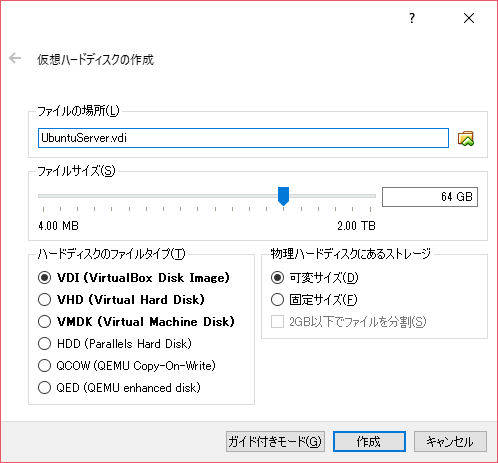

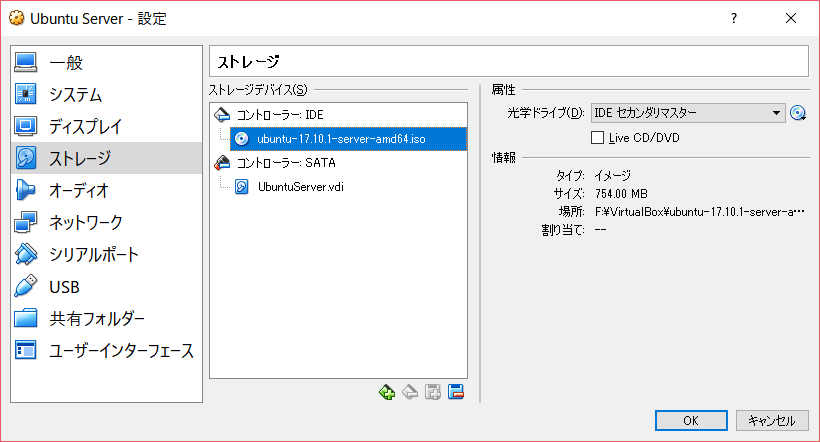

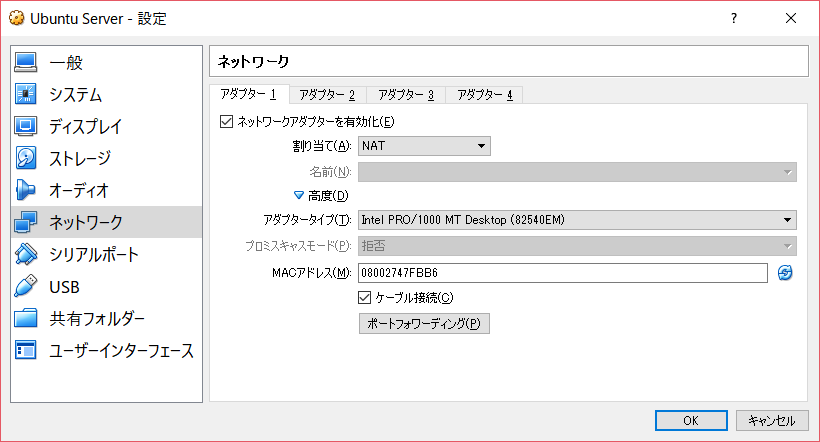

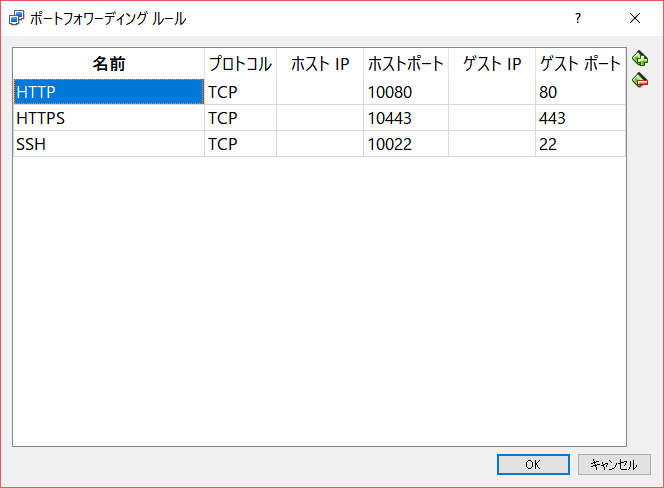

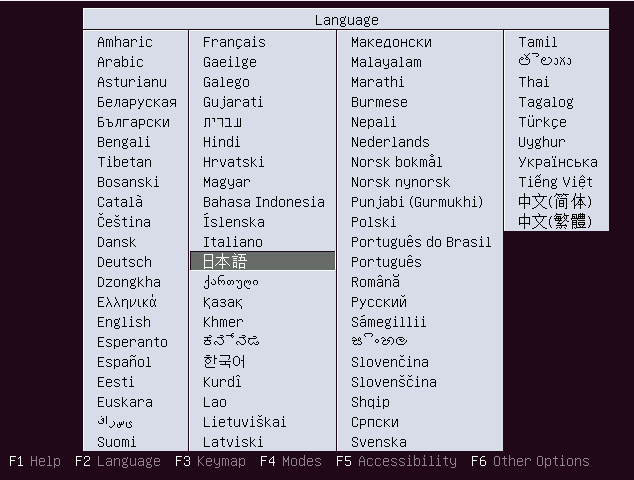

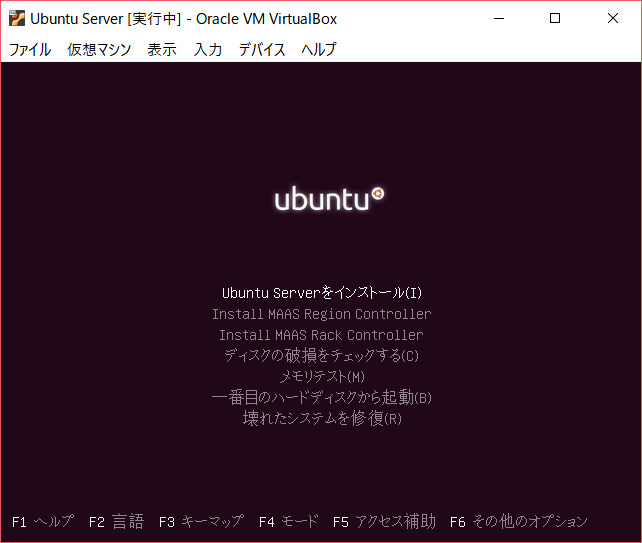

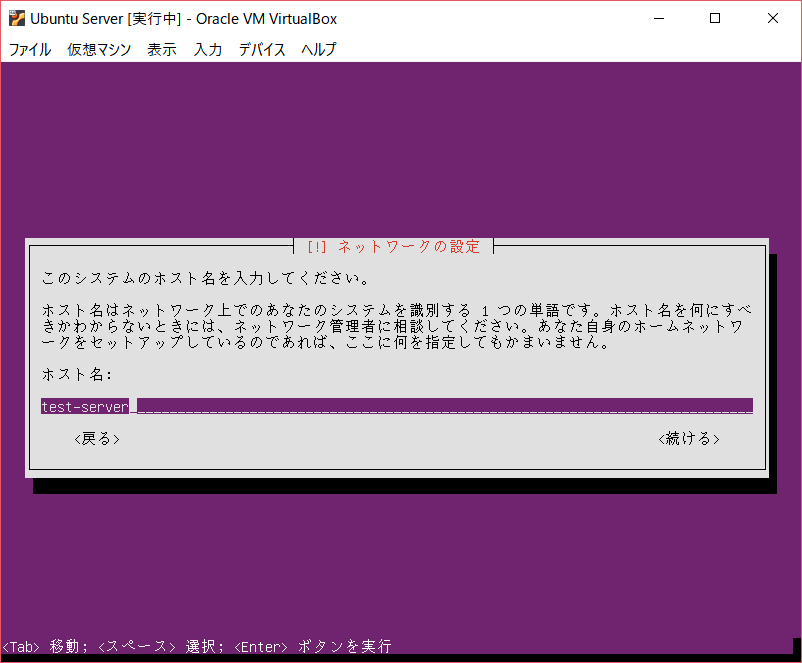

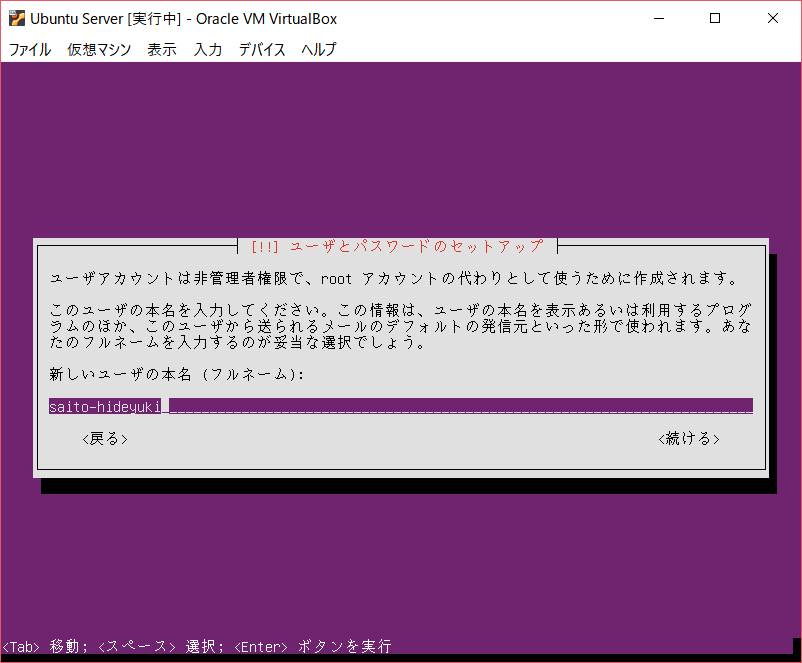

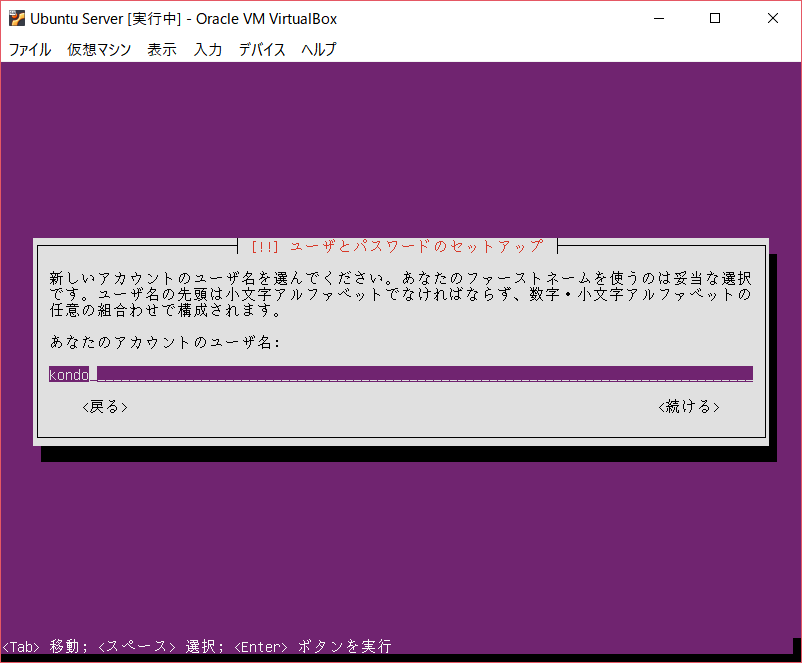

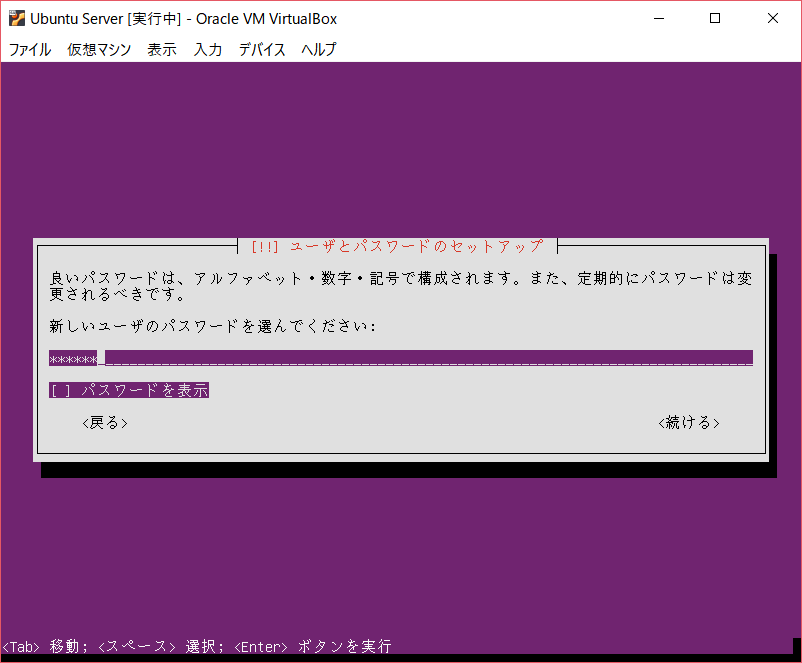

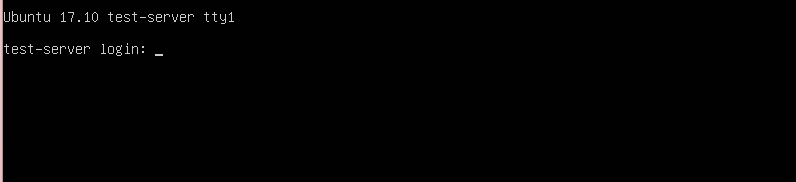

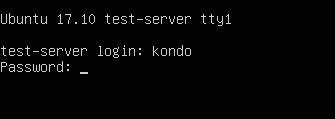

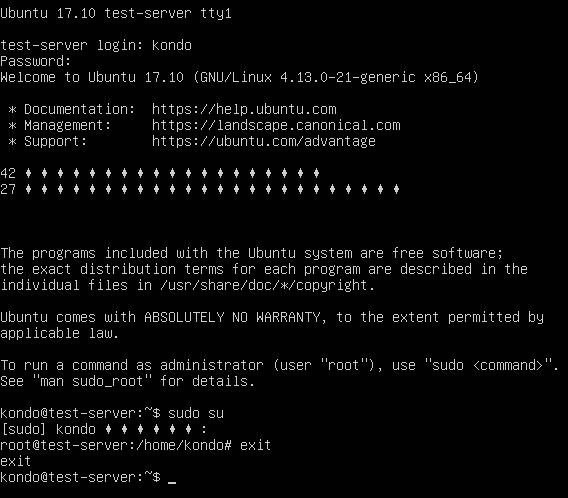

今回はUbuntu仮想環境を使いました。端末で以下を入力してください。CentOSやRed Hat Enterprise Linuxの場合はyumかな。

sudo apt-get install default-jdk

あー、Windowsと違って楽でいいんじゃー。キャプチャ画像とかいらないよね?

もし、管理者権限がない場合でも、JDKのダウンロードページからダウンロードし、適当なところに展開してパスを通せば使うことが出来ます。意味が分からない人は管理者に「JDKと、IntelliJ IDEAを入れてください」と連絡するのが早いです。

IntelliJ IDEAをインストールする

IntelliJ IDEAはChisel開発もできるエディター(メモ帳)です。正確には統合開発環境と言います。

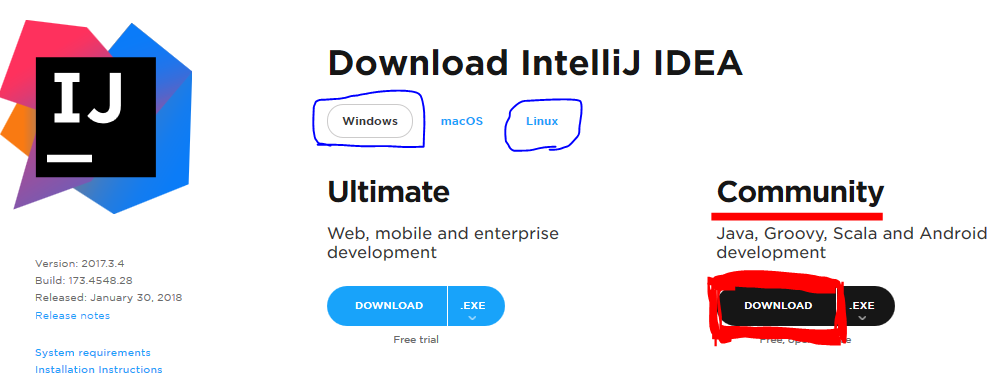

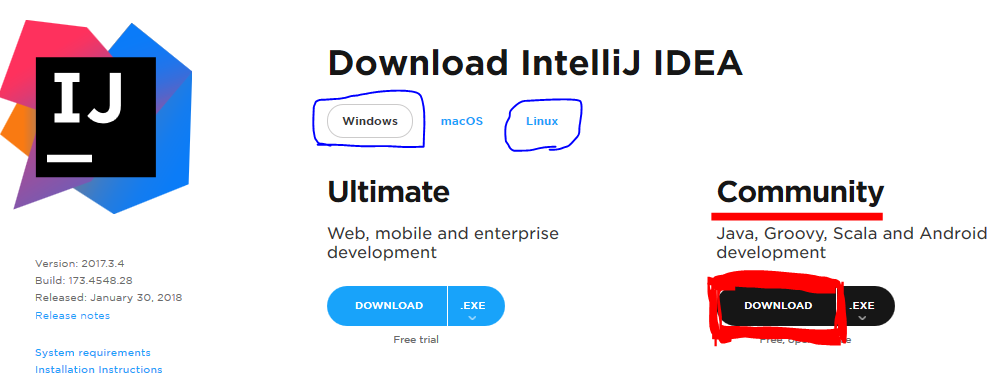

Windowsの人も、Linuxの人もIntelliJ IDEAのダウンロードページからCommunity版(無料)をダウンロードしてください。Ultimate版は有料です。

Windowsの人

インストールをする際に、必ずしも画像と同じにならない場合があります。そういうときは焦らずに、画面に何が書いてあるのかを読んで、理解をしてから、手順を判断してください。

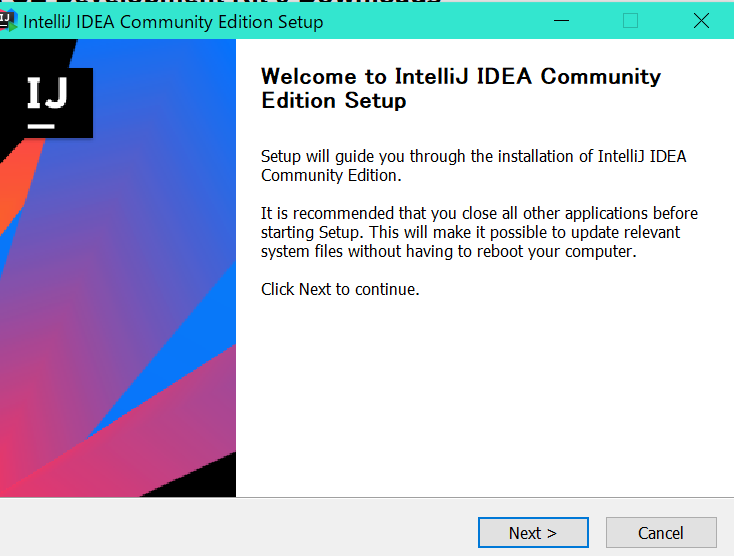

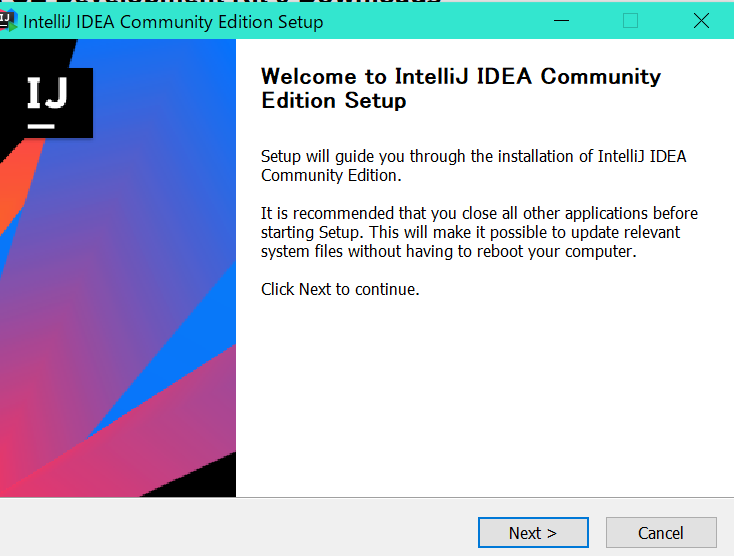

インストーラを起動すると、次の様な画面になりますので、「Next」を押してください

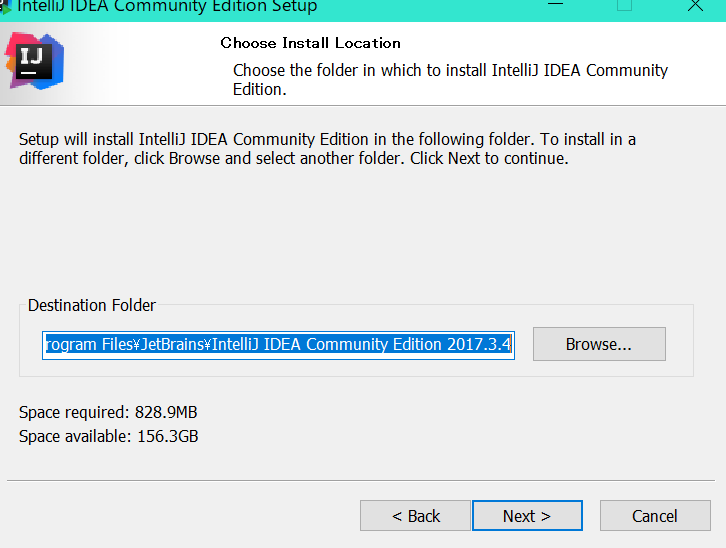

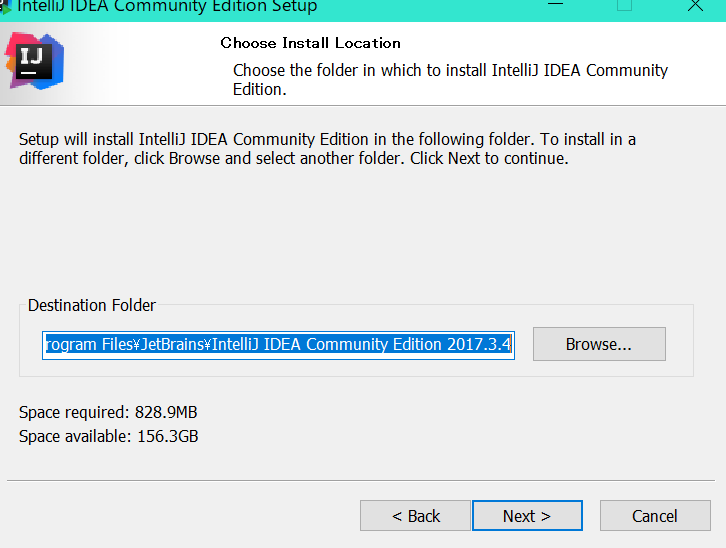

インストールディレクトリを指定します。デフォルトのままで良いので、「Next」を押してください

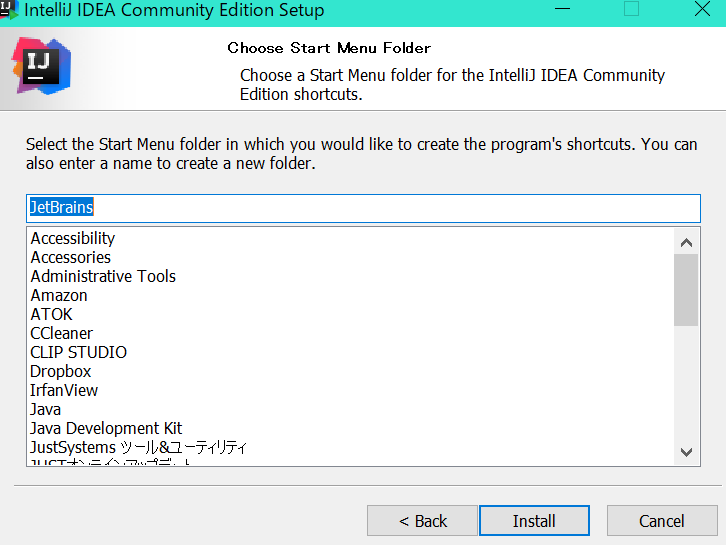

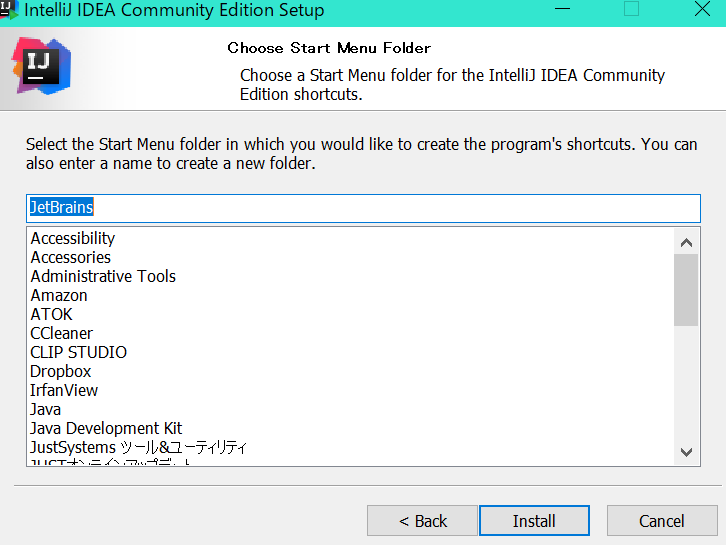

これもそのままで、「Install」を押してください

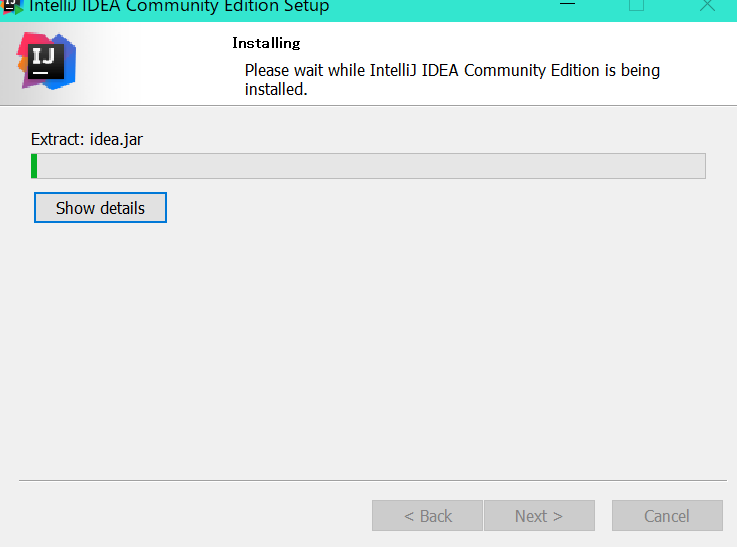

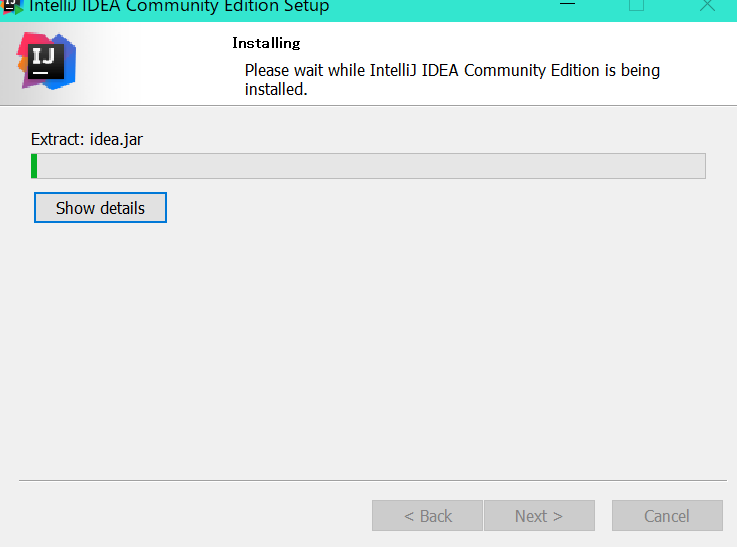

暫く待機します。

お疲れ様です。インストール完了です。後述の「IntelliJ IDEAの初期設定(Windows、Linux共通)」へ進んでください。

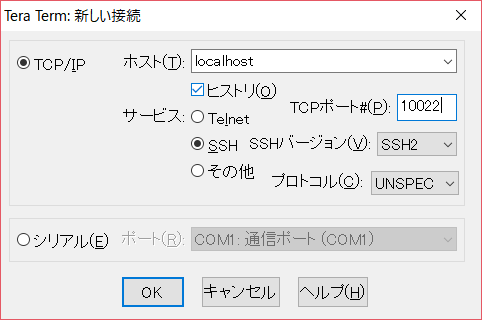

Linux(Ubuntu)の人

ダウンロードしたファイルを適当なディレクトリに展開します。

展開したら、展開したフォルダ/binにPATHを通します。

パスを通したら端末を起動して以下をタイプ。

idea

あー、楽なんじゃー。

IntelliJ IDEAの初期設定(Windows、Linux共通)

IntelliJ IDEAでChiselが開発できるように初期設定を行います。

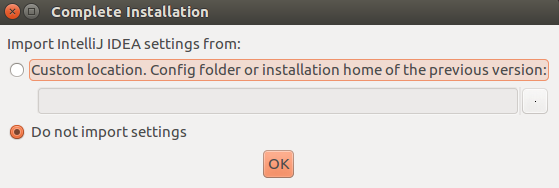

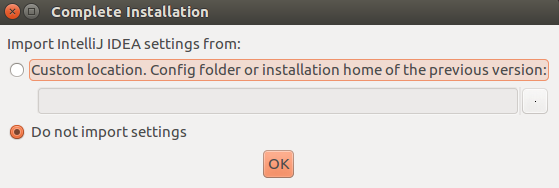

初回起動時は以下の様な質問が聞かれます。(画像はLinux版)設定のインポートはすることないので、「Do not import settings」のままOKを押します。

ライセンスに同意する画面に映るので、全ての条項を読んで、Acceptを押してください。(一番下まで読まないとAcceptは押せません)

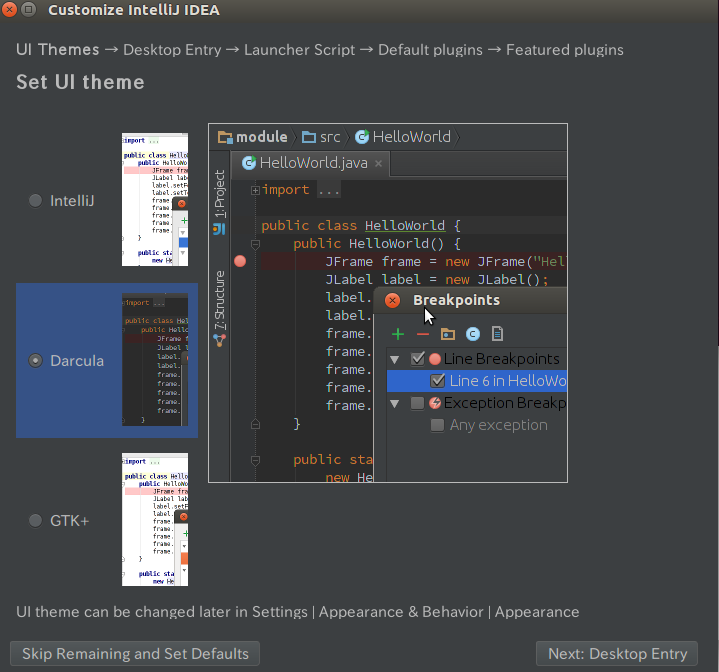

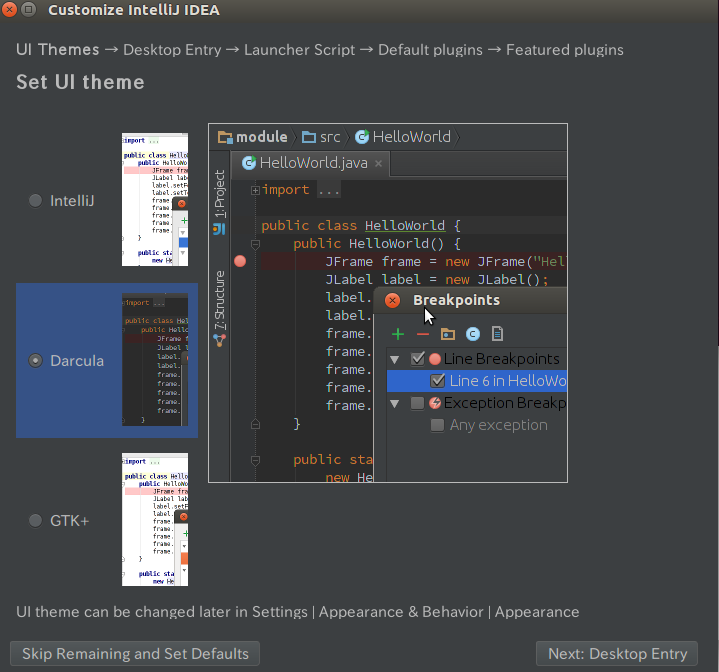

見た目をどうするかを聞かれるので、好きな様に選択してください。私は黒にしました。

※Linuxのみ デスクトップエントリーを作るかどうか聞かれるので好きにしてください。

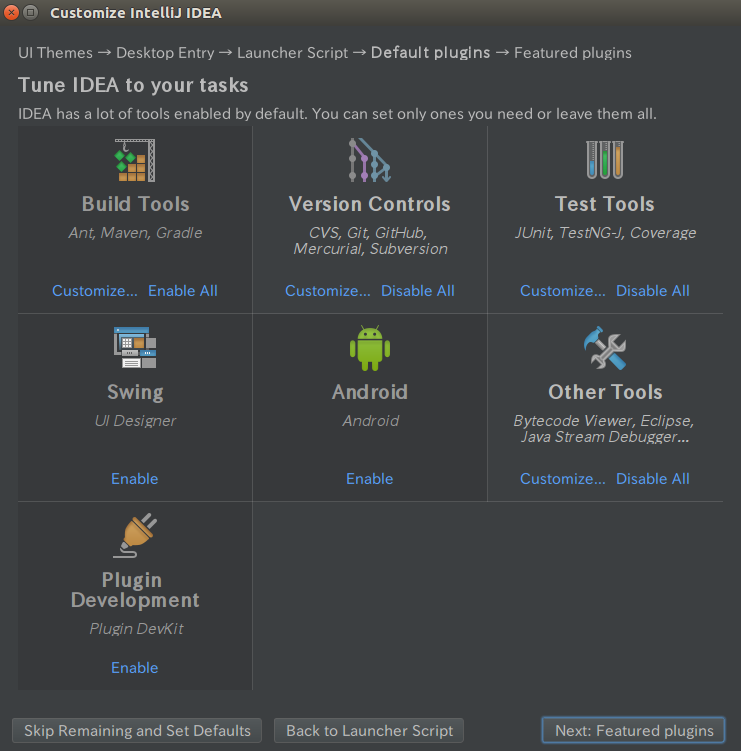

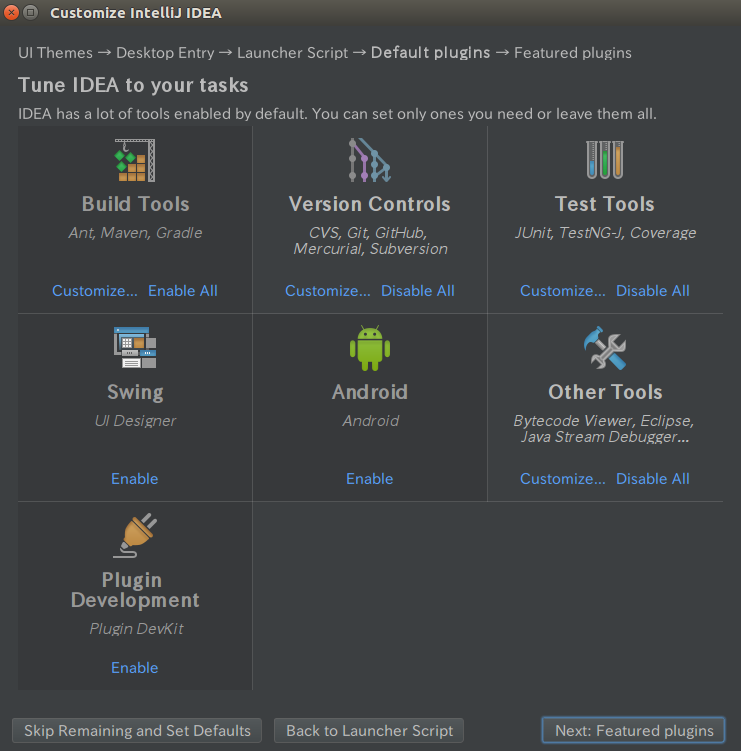

何を有効にするか聞かれます。そのままでも良いですし、画像の様に、Chisel開発に必要ない「Bild Tool」「Swing」「Android」「Plugin Development」はDisableにしても良いです。

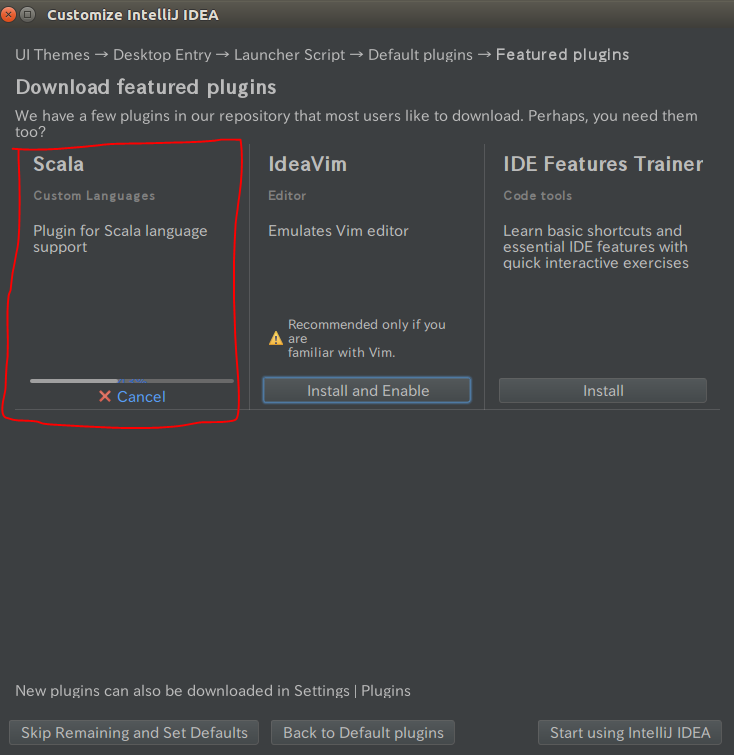

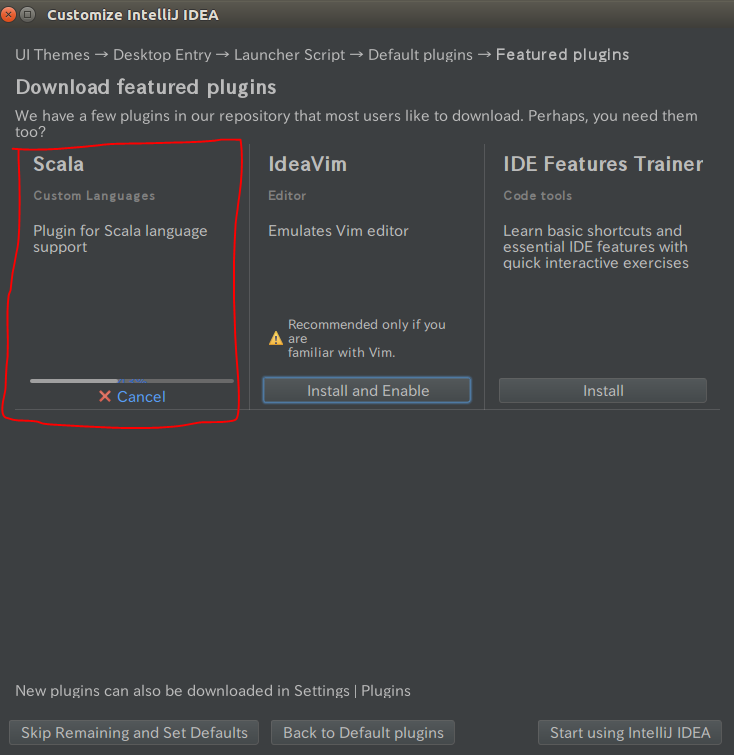

重要 ScalaをInstallしてください。

※プロキシを設定してないと出ません。後からPluginでScalaを入れることも可能です。

以上で初期設定はお終いです。起動画面が立ち上がります。

プロキシが必要ない、もしくは、プロキシ設定しなくてもScalaがインストールできた人は、次のプロキシ環境下:●●の節は飛ばして下さい。

プロキシ設定が必要な人は、次の説も読んでください。

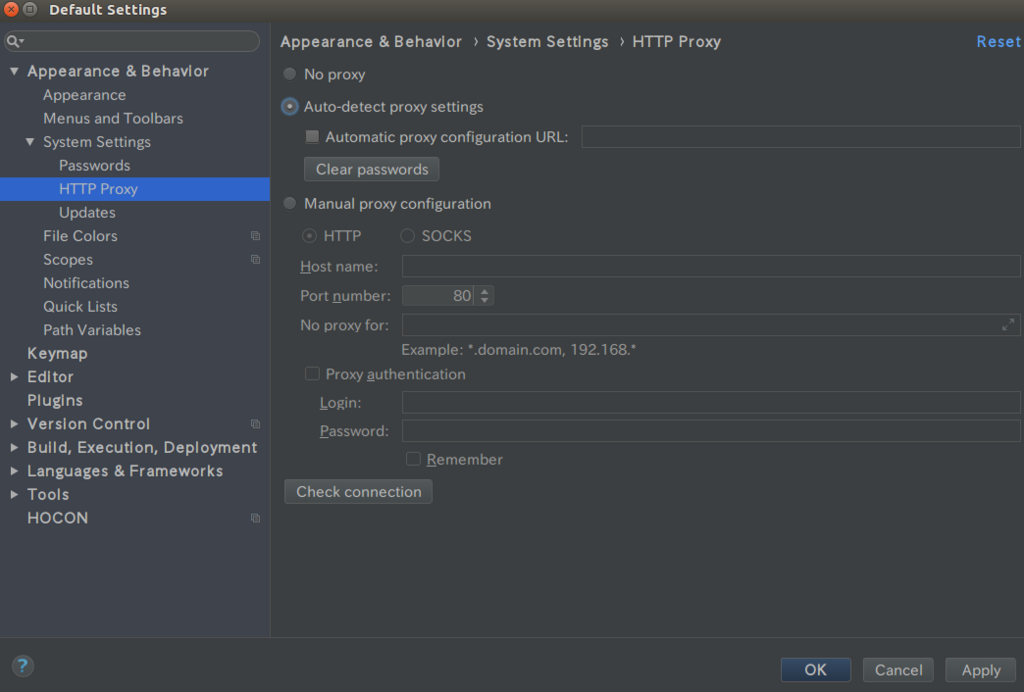

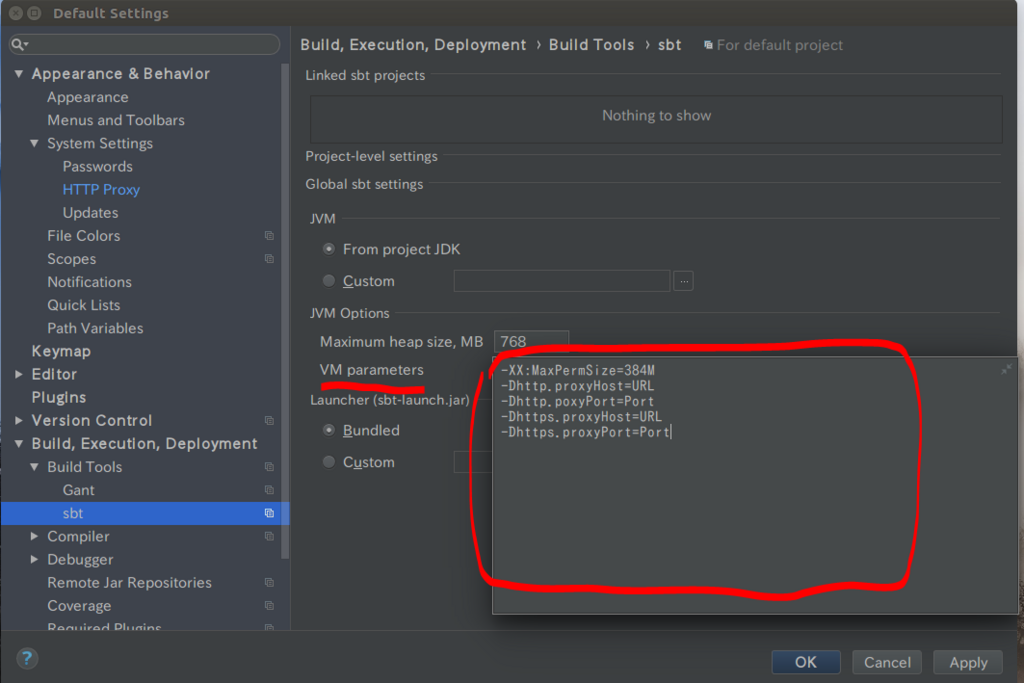

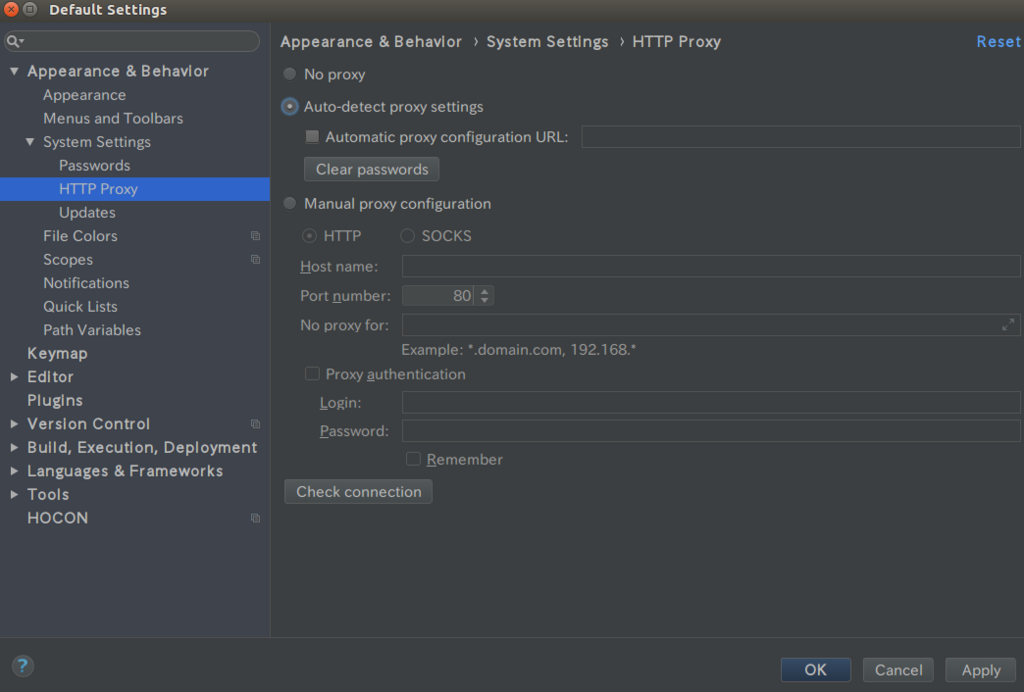

プロキシ環境下:プロキシの設定

会社など、プロキシを通さないといけない環境の人は、プロキシ設定をしてください。プロキシ設定はConfigure→Settingsから開けます。

1. IntelliJ IDEAのプロキシ設定。ご自分の環境に合わせて選択してください。

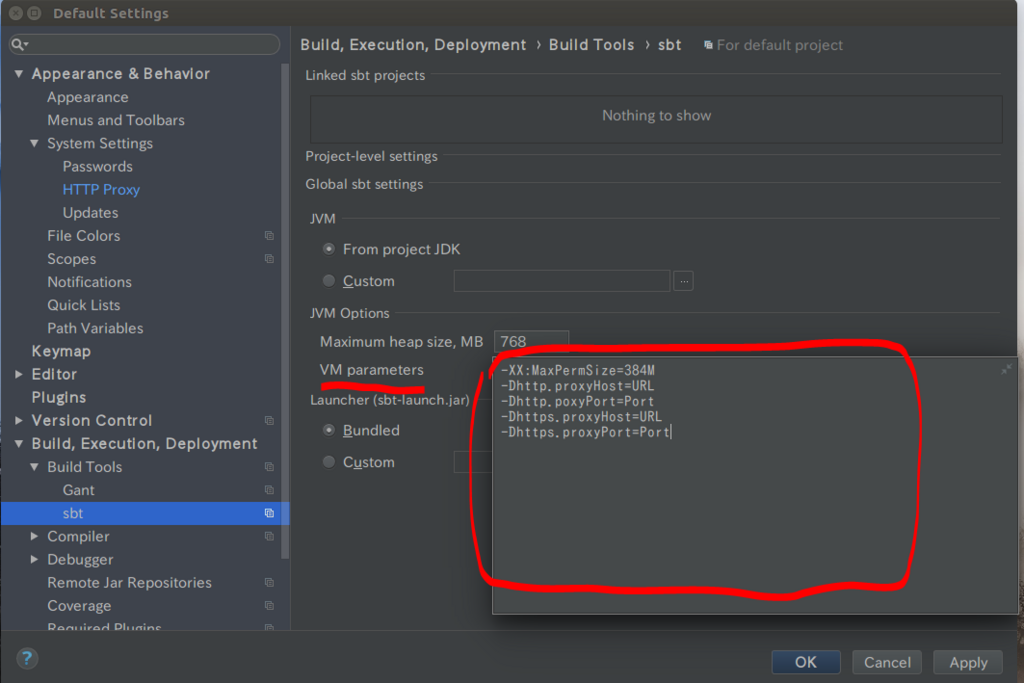

2. Scalaプラグインがをインストール済み:sbtのプロキシ設定。VM parametersにご自身の環境に合わせて以下を入力してください。まだScalaを入れていない場合は、入れてから設定します。(入れ方は後述するので、慌てないでください)

※URLとPortは自分の環境に変えてください

-Dhttp.proxyHost=URL

-Dhttp.poxyPort=Port

-Dhttps.proxyHost=URL

-Dhttps.proxyPort=Port

ユーザー名、パスワードが必要な場合は、-Dhttp.proxyUserと-Dhttp.proxyPassword、-Dhttps.proxyUser、-Dhttps.proxyPasswordも追加。

プロキシ環境下:プロキシが認証局証明書を上書きする場合

プロキシがHTTPSなどの証明書を勝手に妙な証明書に変えてる場合なんかは、かなり面倒です。糞ニートを名乗ってるのに、まるで体験した様な書き方ですね。(遠い目

こういう環境かどうかはFirefoxを入れてみて、Googleが開けるか確認してみてください。開けなければ妙な証明書に書き換えています。

こういう場合は、JDKと、IntelliJの中にあるJREにkeytoolを使って認証局証明書を登録するという作業をする必要があります。

が、上↑の文章意味分からないですよね。大丈夫です、情強を名乗ってる人でもほとんど分かりません。

分かる部署に押しつけましょう。

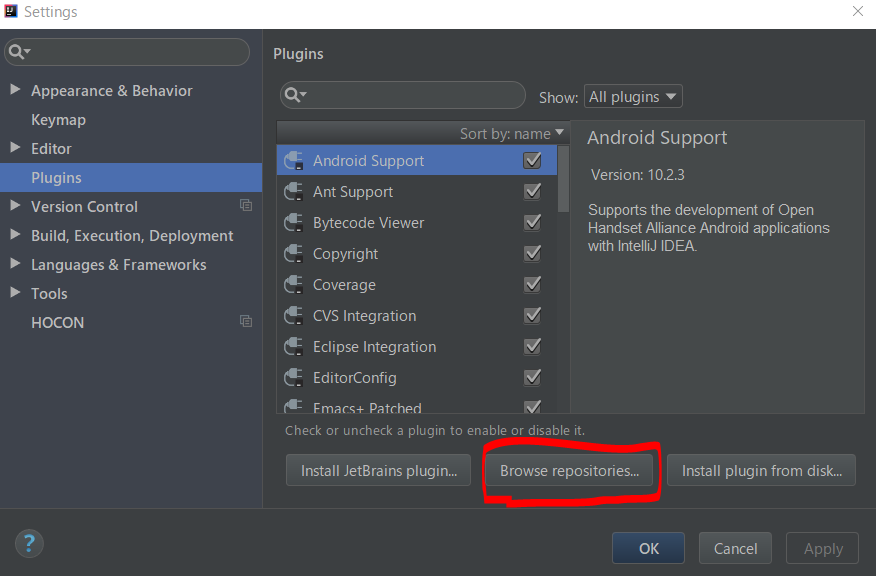

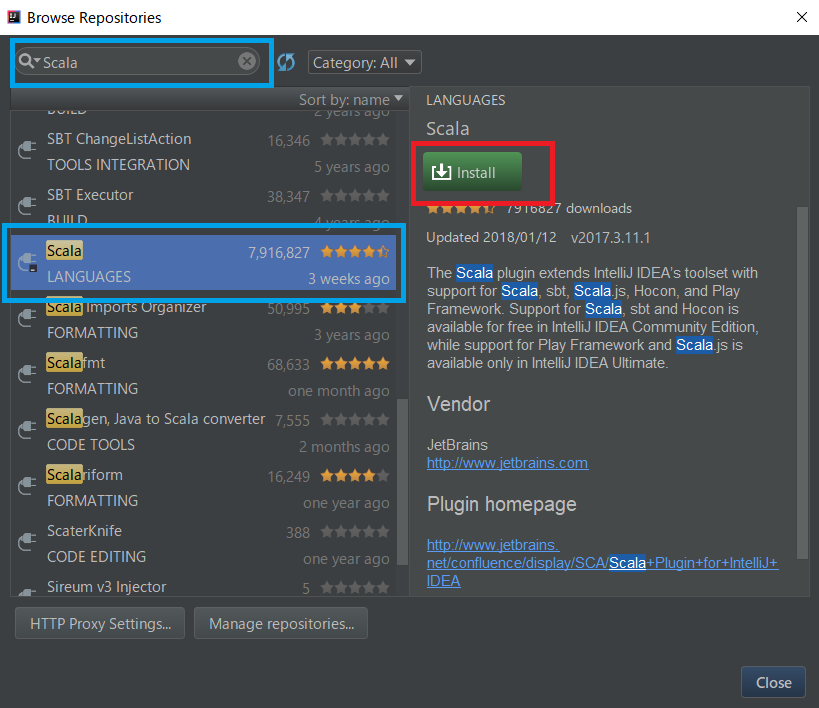

プロキシ環境下:Scalaプラグインを入れる

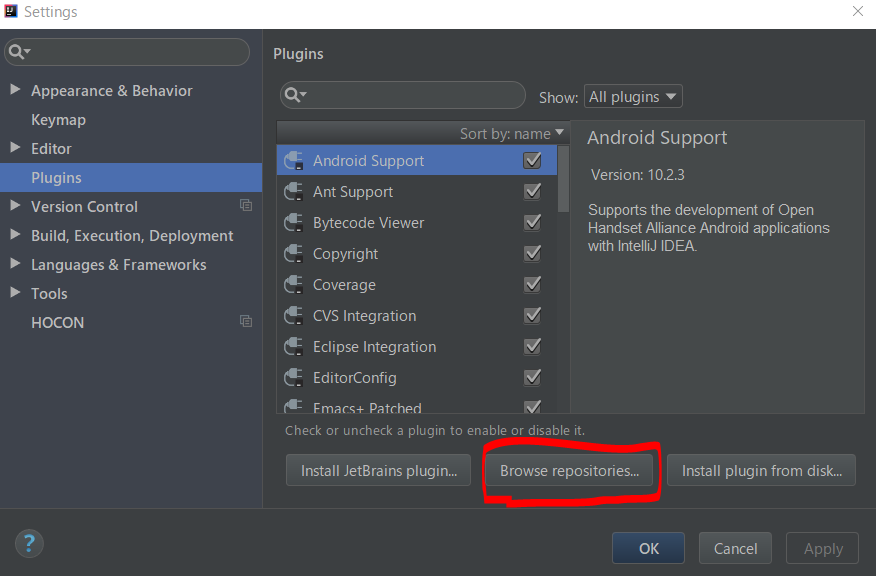

プロキシ設定をしてなかったせいで、最初にScalaを入れられなかった場合は、Scalaプラグインを入れてください。プロキシ設定の時と同じく、Configure→Settingsで設定画面を開きます。

Pluginの項目を開いたらBrowse repositories...をクリックしてください。

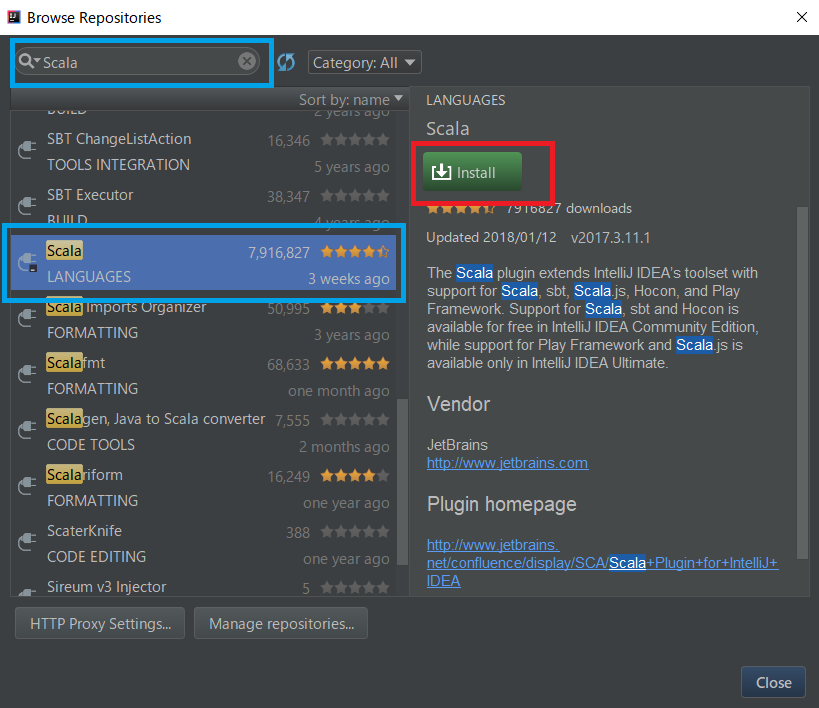

Scalaというプラグインを探し、Installをしてください。検索ボックスにScalaと打ち込むと探しやすくなります。

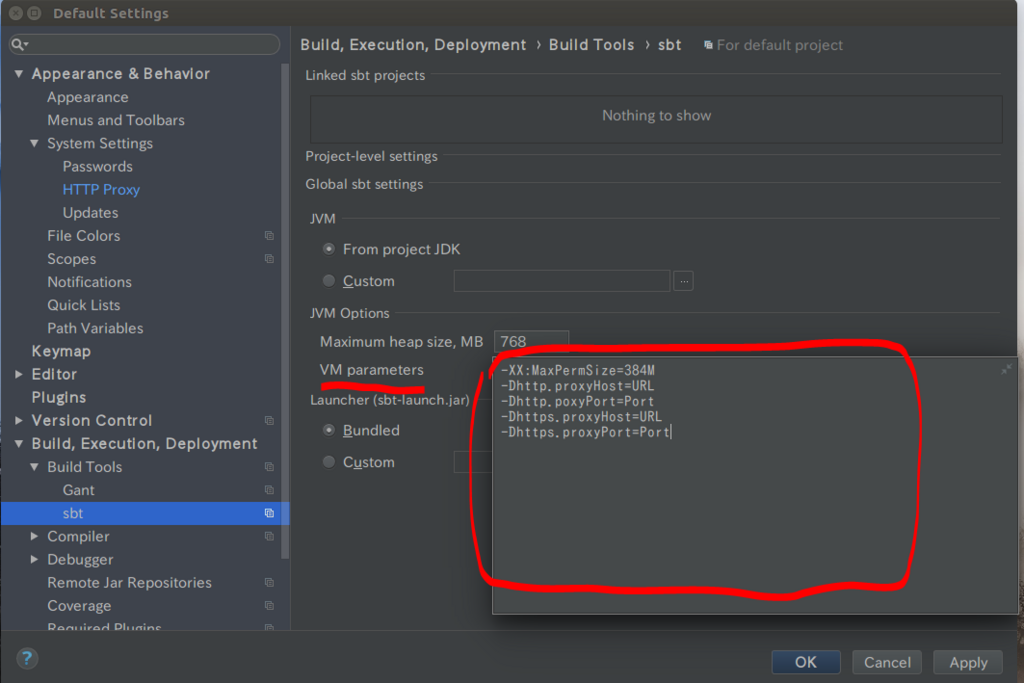

入れたら、sbtのプロキシを設定します。VM parametersにご自身の環境に合わせて以下を入力してください。(再掲)

※URLとPortは自分の環境に変えてください

ユーザー名、パスワードが必要な場合は、-Dhttp.proxyUserと-Dhttp.proxyPassword、-Dhttps.proxyUser、-Dhttps.proxyPasswordも追加。

-Dhttp.proxyHost=URL

-Dhttp.poxyPort=Port

-Dhttps.proxyHost=URL

-Dhttps.proxyPort=Port

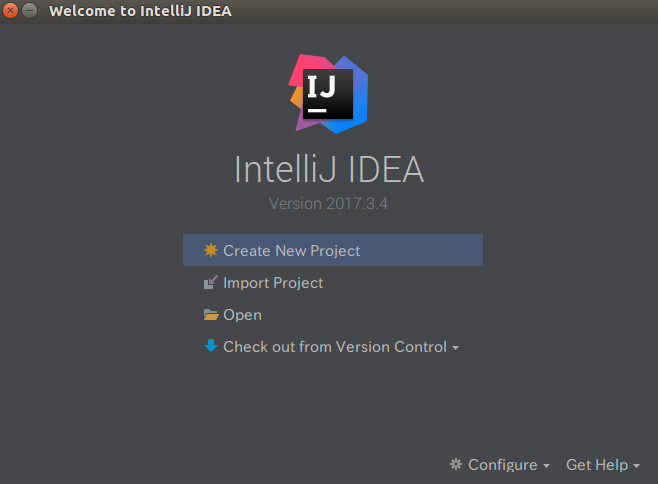

IntelliJ IDEAでChiselを動かしてみる

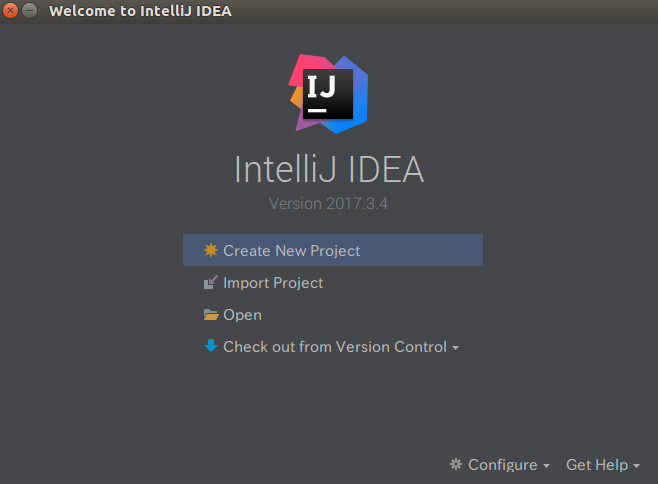

IDEAが起動すると、以下の様な画面になります。とりあえず、「Create New Project」をクリックしてください。

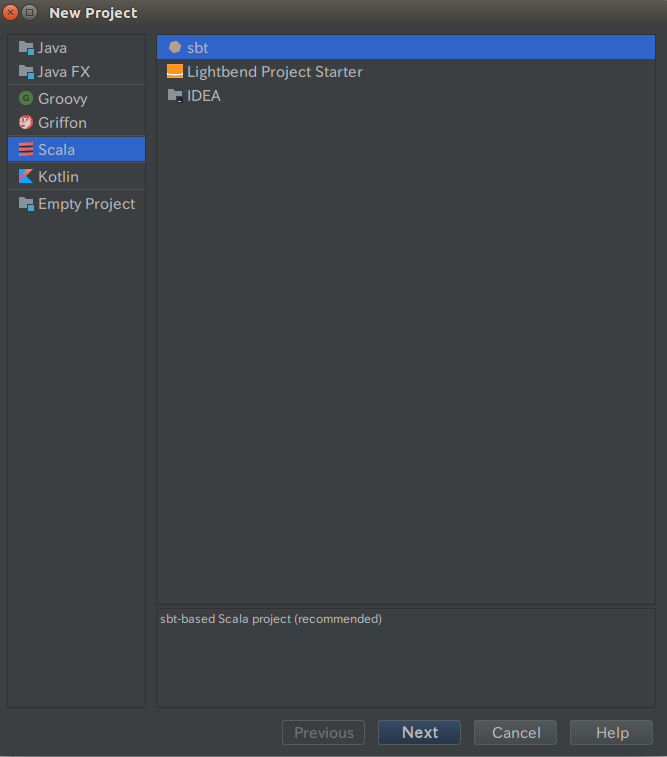

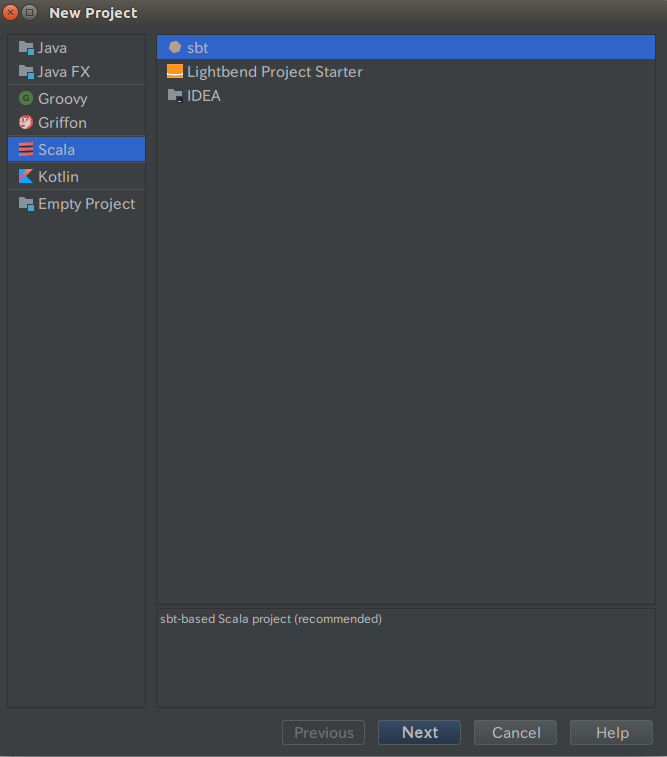

Scala→sbtと選択し、「Next」ボタンを押してください

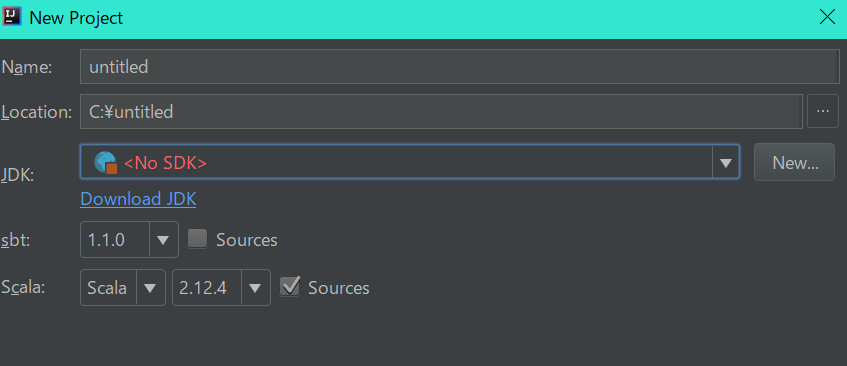

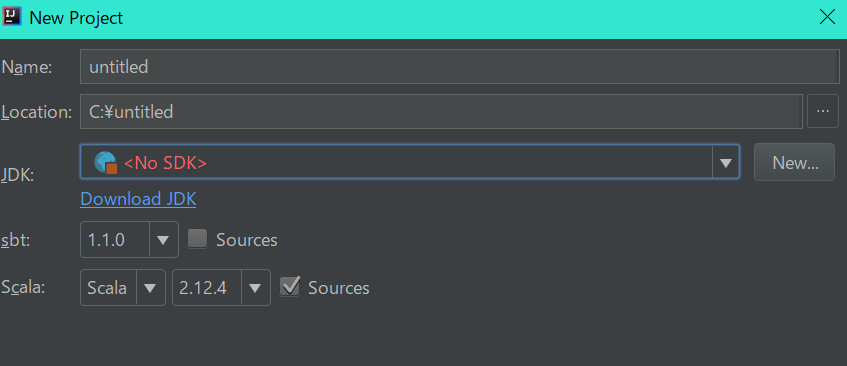

Nameにプロジェクト名を適当に入れてください。保存場所が気に入らなければLocationを適当に変更してください。Windowsの人はもう一つすることがあるので、まだFinishを押さないでください。Linuxの人はFinishを押してください。

※Windowsの人のみ

Windowsの場合、JDKが自動的に入力されません。なので、自分で最初にインストールしたJDKを教える必要があります。

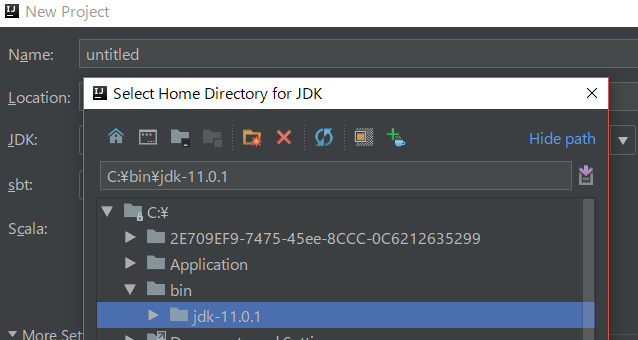

※Windowsの人のみ

JDKの横にあるNewボタンを押すと、ポップアップが開くので、インストールしたJDKを選択してください。その後、Finishを押すと、プロジェクトが作成されます。

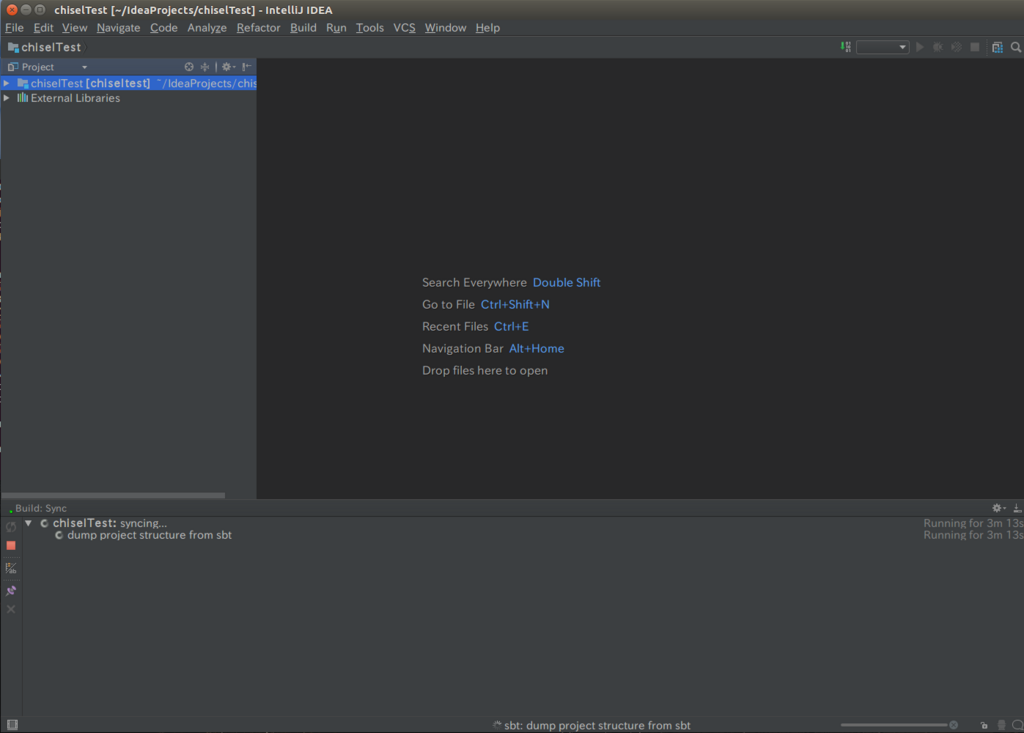

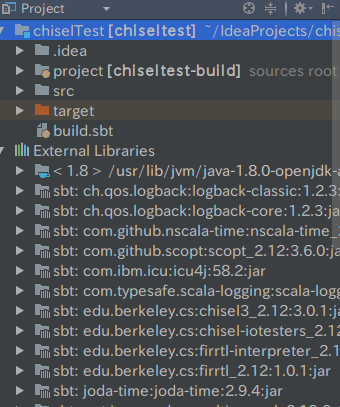

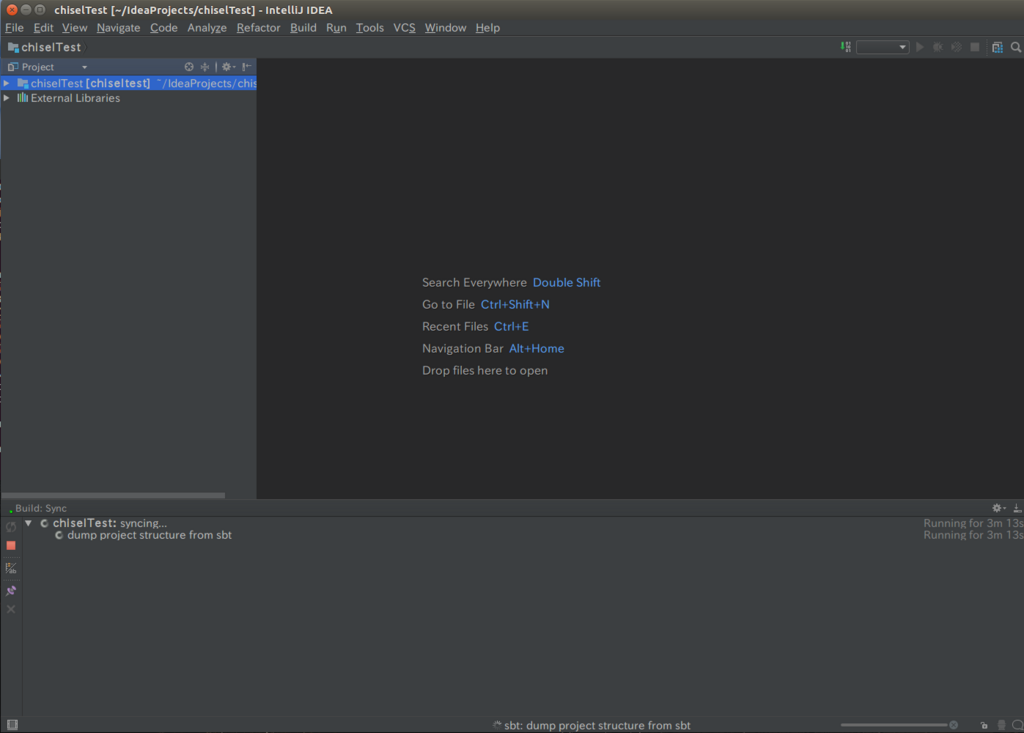

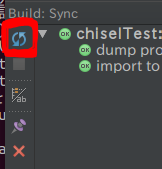

しばらくすると以下の様な画面になります。初回はかなり時間かかりますから、コーヒーでも飲んでてください。

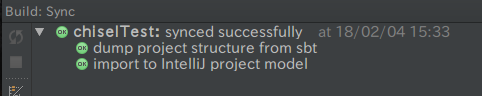

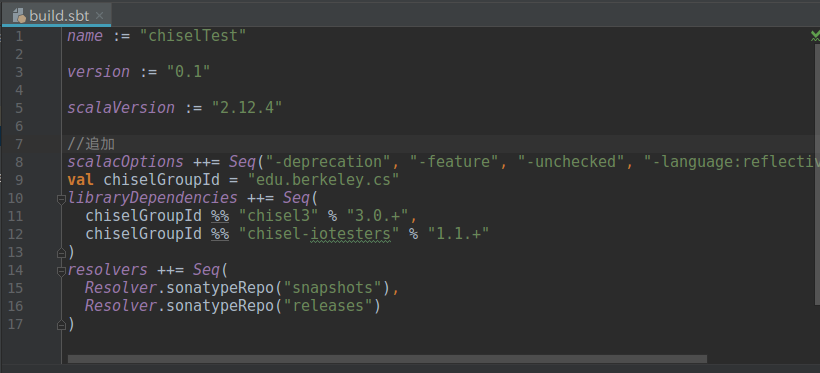

下でクルクル回ってた奴が、こんな感じになればOKです。

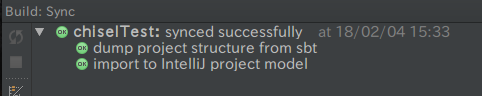

左上にあるProjectの中から、build.sbtを探してダブルクリックします。

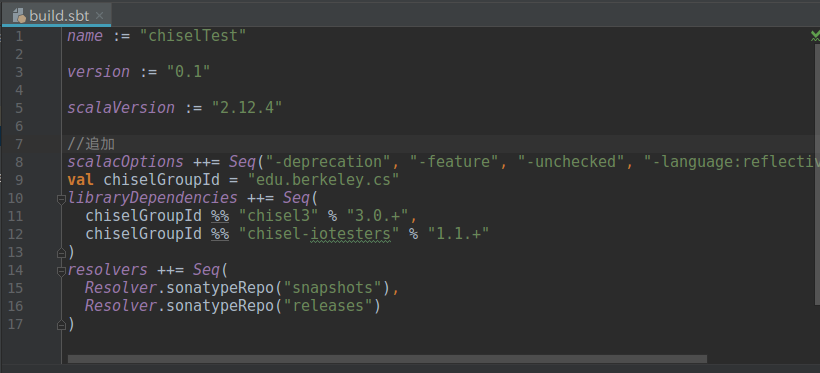

build.sbtに以下の内容を追加してください。この設定を書くことで、このプロジェクトでChisel3が使える様になります。なお、この記事はChisel3.0の時代の記事なので、3.1とか3.2とか、4.0とかが出ていたら、libraryDependenciesを必要に合わせて変更してください。GitHub - freechipsproject/chisel3: Chisel 3で確認できます。

scalacOptions ++= Seq("-deprecation", "-feature", "-unchecked", "-language:reflectiveCalls")

val chiselGroupId = "edu.berkeley.cs"

libraryDependencies ++= Seq(

chiselGroupId %% "chisel3" % "3.0.+",

chiselGroupId %% "chisel-iotesters" % "1.1.+"

)

resolvers ++= Seq(

Resolver.sonatypeRepo("snapshots"),

Resolver.sonatypeRepo("releases")

)

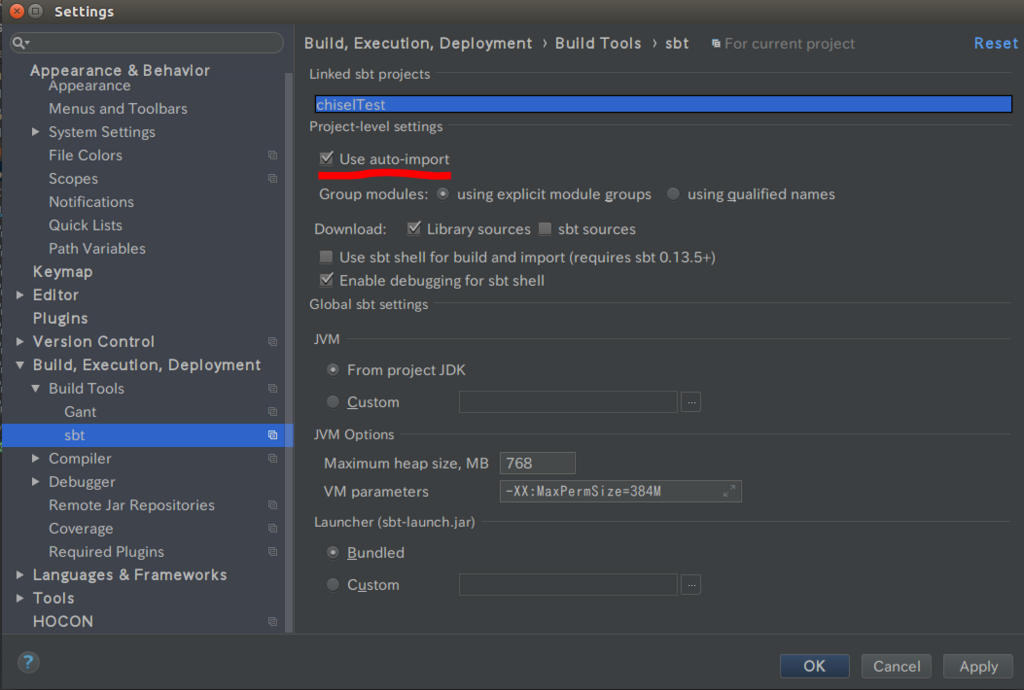

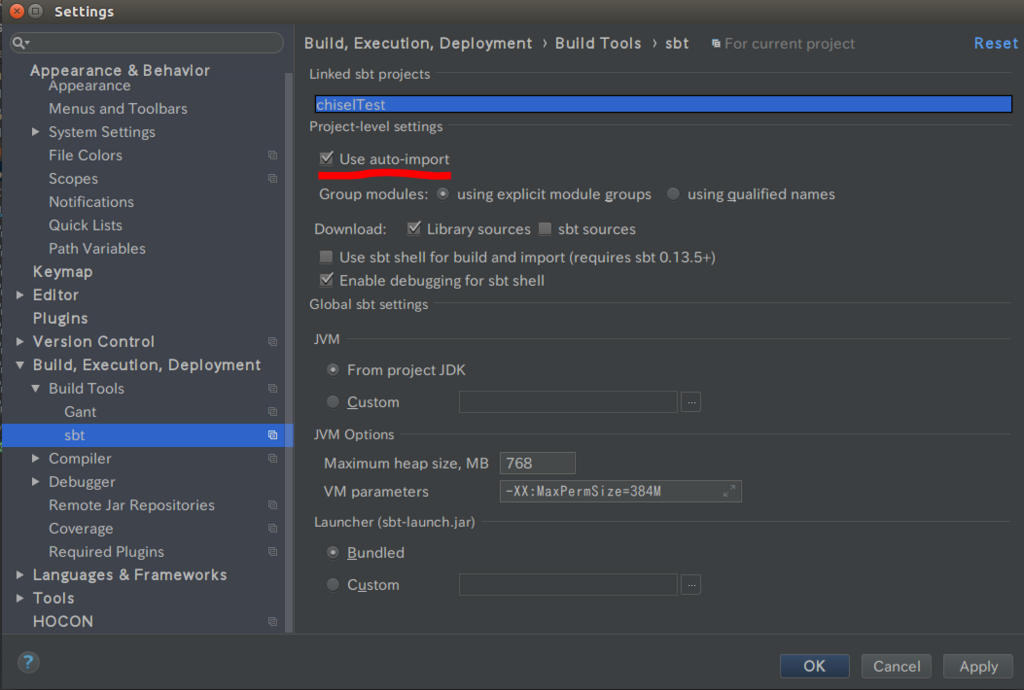

ファイルを保存すると、Linuxだったら上の方に、Windowsだったら下の方(?あやふや)に「Use auto-import」がうんうん、とかいう質問が出てくると思う(ごめん、キャプチャ忘れてた)ので、「Use auto-import」を有効化してください。

出てこない、よく分からん、私の様に見逃したという人は、メニューバーのFile→Settingsをクリックして設定画面を開き、sbtの項目を開いて、「Use auto-import」にチェックを入れてください。

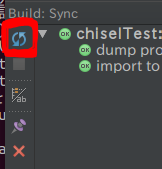

先ほどクルクル回ってた奴の横にある、リロードみたいなボタンを押します。 再び処理にかなり時間がかかるので、お茶でも飲んで待っててください。

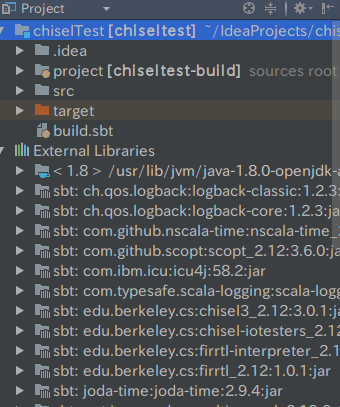

処理が完了すると、External Library(外部ライブラリ)の項目がずらっと増えます。これで、プロジェクト内でChisel3が使える様になりました。

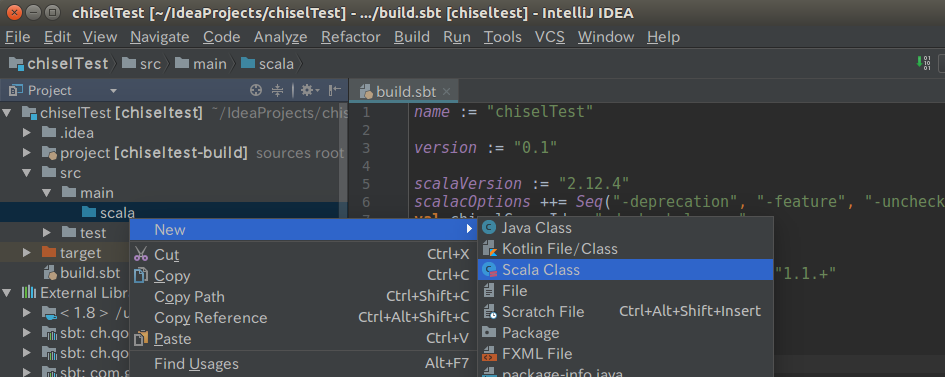

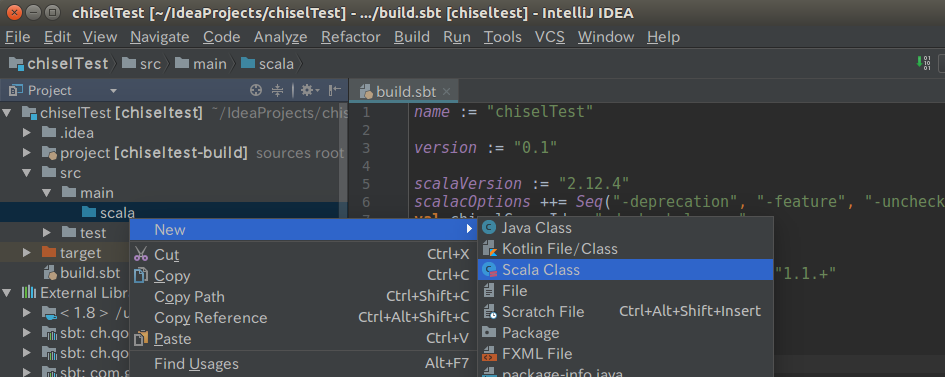

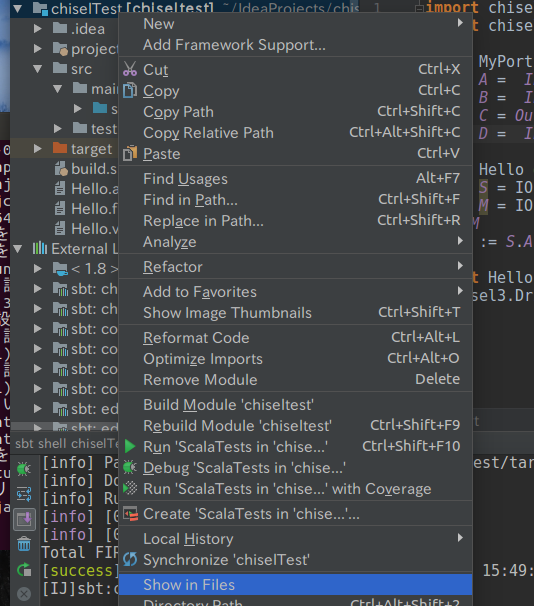

プロジェクトのsrc/main/scalaフォルダを右クリックし、ポップアップメニューの中からNew→Scala Classを選択します。

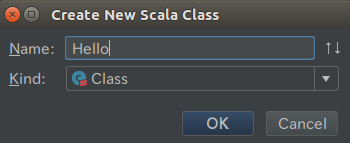

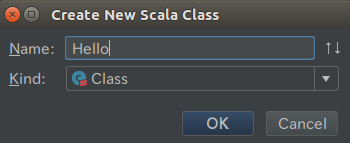

Helloと入力し、OKをクリックします。

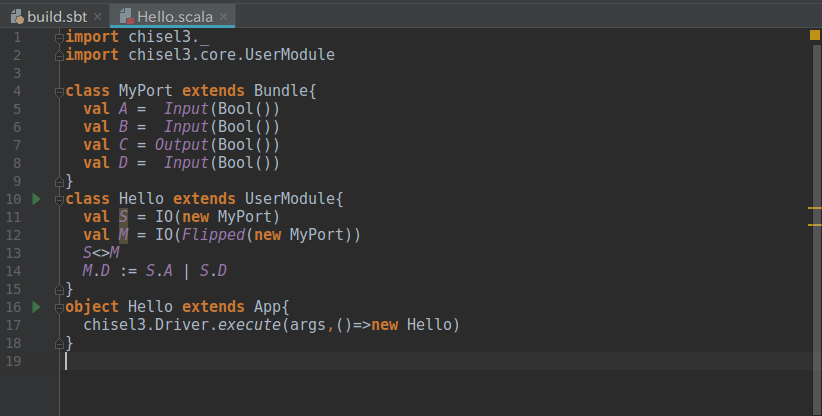

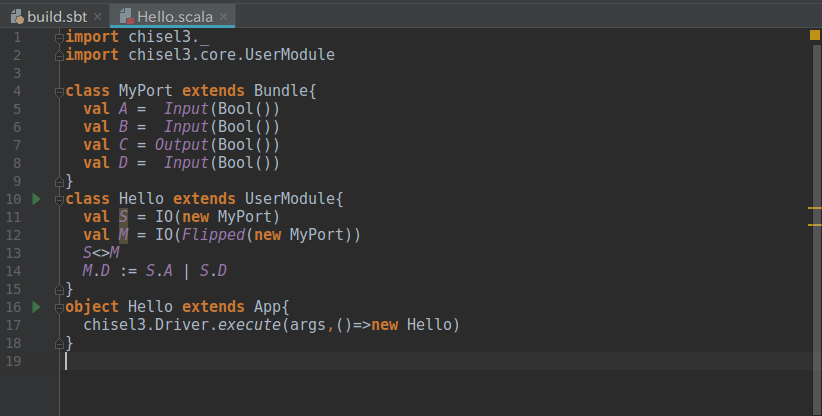

Hello.scalaが作成されてエディタが開くので、以下の内容を打ち込んでください。前回脳汁飛ばしながら紹介したコードです。

import chisel3._

import chisel3.core.UserModule

class MyPort extends Bundle{

val A = Input(Bool())

val B = Input(Bool())

val C = Output(Bool())

val D = Input(Bool())

}

class Hello extends UserModule{

val S = IO(new MyPort)

val M = IO(Flipped(new MyPort))

S<>M

M.D := S.A | S.D

}

object Hello extends App{

chisel3.Driver.execute(args,()=>new Hello)

}

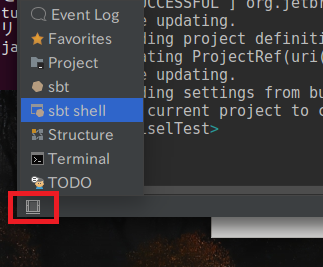

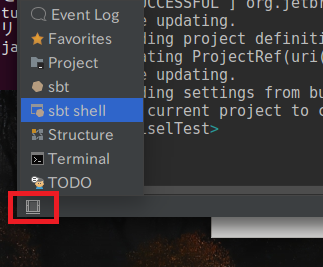

次に、sbt shellを開きます。sbt shellという文字が画面内に見つからない場合は、画面左下の四角いボタンを押して、sbt shellを選択してください。

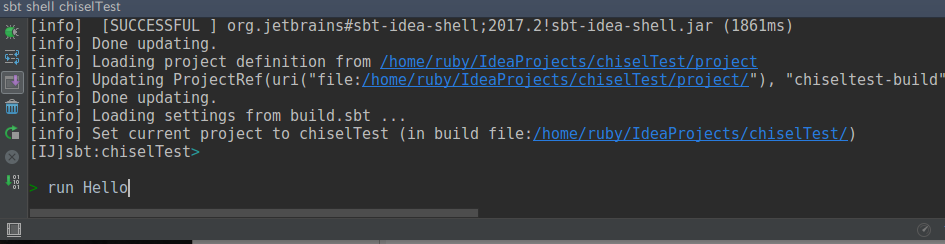

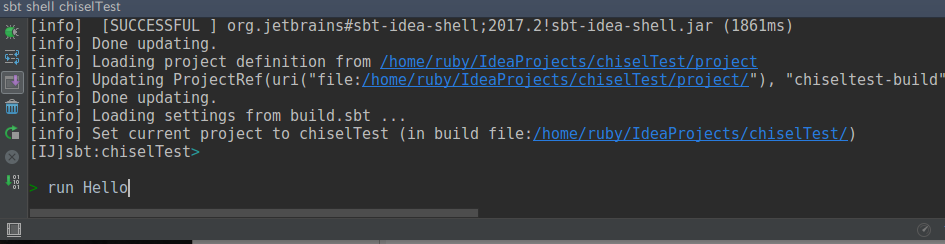

sbt shellが暫く立ち上がるのに時間がかかります。動きが止まって [IJ]sbt:プロジェクト名> という文字が出たら立ち上がり完了です。

立ち上がりを確認したら、Chiselを動かしてみましょう!

「run Hello」と打ち込んで、Enterを押してください。

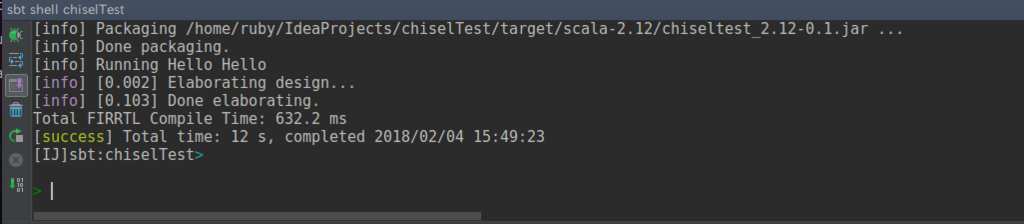

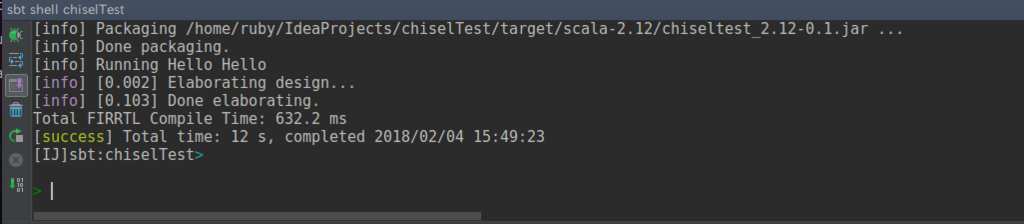

問題が起こらなければ、以下の図の様に [success ] の文字が出てきます。

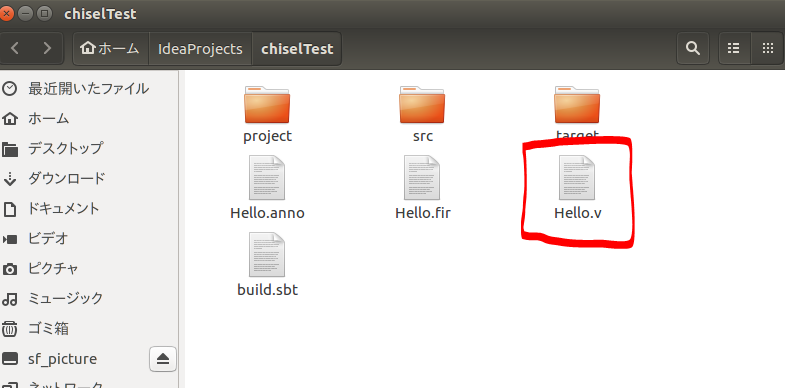

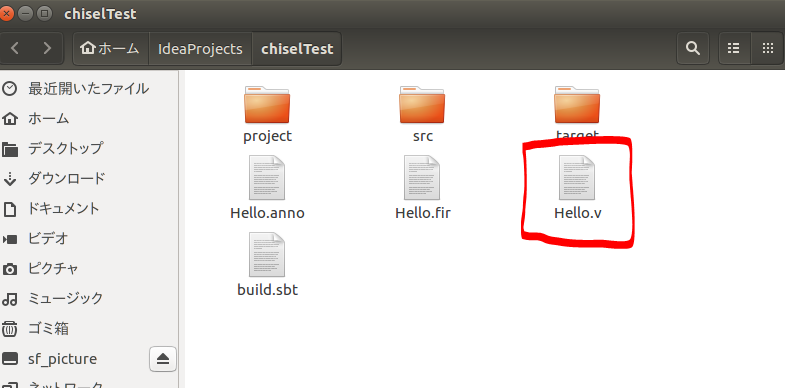

では、実際に生成されたVerilogファイルを見てみましょう。

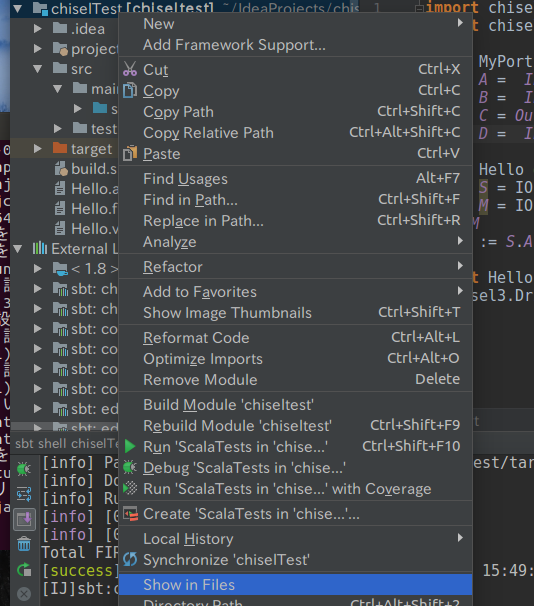

プロジェクトを右クリックして出てくるポップアップメニューから、Windowsなら「Show in Explorer」を、Linuxなら「Show in Files」を選択してください。

すると、プロジェクト内にHello.vというファイルが生成されているはずです。できてますよね!?おめでとうございます!

実際に中身を開いてみるとこのようなVerilogファイルになっていました。

`ifdef RANDOMIZE_GARBAGE_ASSIGN

`define RANDOMIZE

`endif

`ifdef RANDOMIZE_INVALID_ASSIGN

`define RANDOMIZE

`endif

`ifdef RANDOMIZE_REG_INIT

`define RANDOMIZE

`endif

`ifdef RANDOMIZE_MEM_INIT

`define RANDOMIZE

`endif

module Hello(

input S_A,

input S_B,

output S_C,

input S_D,

output M_A,

output M_B,

input M_C,

output M_D

);

wire _T_13;

assign _T_13 = S_A | S_D;

assign S_C = M_C;

assign M_A = S_A;

assign M_B = S_B;

assign M_D = _T_13;

endmodule

おわりに

いかがでしたでしょうか。

JDKとか言う謎の物と、IntelliJをインストールさえすれば、開発開始出来るので意外と簡単だったのではないでしょうか?

まぁ、この記事書いた私はすっげー疲れましたが。

Chisel開発の最初のインストールの段階で躓く、ということが、この記事で解消出来たなら幸いです。

続きを読む