Zynq をVitisで Lチカするまでの簡単な手順書

Vitis の起動の仕方すらわからないんだけど

おもむろに Vitis を起動してみたらこんな画面が出てきた。

え………っと、え?何語?日本語でおk。読めない。

ていうか、え?何?私はC++をコンパイルして動かしたいだけなんだけど………。

何でこんなにボタンいっぱいあるの?意味わからない。コワイ。

というわけで、当方初 Vitis で Cora Z7 07Sで Lチカするのに6時間も Vitis の起動方法が分からなくて格闘したのでその記録です。

Vitis むつかしすぎる………。世の中の人、これを当たり前に使ってるのすごいよ………。

Git プロジェクト

作ったものはこちらにあります。

1. Vivado のデザインを作る

Cora Z7 07S は Zynq なので、中に ARM CPU が載っています。これを使って L チカをする………といっても、まずはベースとなるデザインが必要らしいです。

なので、単純に ARM CPU と LED (GPIO)を接続しただけのデザインを作ります。

1.1 Git Ignore を作成

まずは .gitignore を作ってコミットします。

build*/ .vscode/

my_first_vitis_prj/.gitignore at master · nodamushi/my_first_vitis_prj · GitHub

1.2 CMakeLists.txt を作成

次に、Vivado のプロジェクトを作成、合成するための CMake を作成していきます。

CMake で Vivado を扱うにはなんかGitHubに転がってたゴミでできるみたいです。

CMakeLists.txt を作成して、おもむろに以下のコードをコピペ

- ※ VIVADO_REQUIRED_VERSION は自分のVivado のバージョンに合わせる

- ※ GIT_TAG のバージョンだけは最新を調べて設定

- ※ project名はご自分のものに変更

cmake_minimum_required(VERSION 3.14) project(my_first_vitis_prj) ################## # Vivado Version # ################## set(VIVADO_REQUIRED_VERSION 2021.1) #### おまじない ########## include(FetchContent) # https://github.com/nodamushi/vivado_cmake_module FetchContent_Declare( vivado_cmake_module GIT_REPOSITORY https://github.com/nodamushi/vivado_cmake_module.git GIT_TAG v0.0.6 # バージョンは最新のを使う ) FetchContent_MakeAvailable(vivado_cmake_module) list(APPEND CMAKE_MODULE_PATH ${vivado_cmake_module_SOURCE_DIR}) find_package(HLS) find_package(Vivado) find_package(Vitis) ############################

したらば、ターミナルを開いて、以下のコマンドを実行してみましょう。

mkdir build cd build cmake ..

エラーが出なければOK。

通常のインストールフォルダとは異なる場所に Vivado をインストールしたなど、 Vivado が見つからないエラーが出る場合は -DVIVADO_ROOT オプションを指定する。

cmake -DVIVADO_ROOT=/hoge/moge/Xilinx/Vivado/2021.1 ..

1.3 CMakeLists に Vivado プロジェクトを追加

続いて、CMakeLists.txt に以下を追加します。

FetchContent_Declare( xilinxboardstore GIT_REPOSITORY https://github.com/Xilinx/XilinxBoardStore.git GIT_TAG d4e7c68d16042b32a88790162d9b2b5642ca476b ) FetchContent_MakeAvailable(xilinxboardstore)

………コワイ。何してるのかよくわからない。

今回、私が使ってるボードは Cora Z7-07S なのですが、これって最近の Vivado からボード定義ファイルが削除されたんですよね。

なので、GitHub - Xilinx/XilinxBoardStore からダウンロードしてくる処理を最初に書いています。

コワイ FetchContent_Declare と FetchContent_MakeAvailable がそのダウンロード処理です。

Vivado に最初から定義されているボードを使う場合は不要です。

次に、ようやく Vivado プロジェクトを追加します。

add_vivado_project ( sample_design # プロジェクト名 DESIGN top.tcl # デザインファイル TOP top_wrapper # トップモジュール名 (デザインファイルから自動生成) BOARD digilentinc.com:cora-z7-07s:part0:1.0 # Cora Z7-07S を使用 BOARD_REPO ${xilinxboardstore_SOURCE_DIR} # ↑でダウンロードした XilinXBoardStoreへのパスを追加 )

add_vivado_project で Vivado のプロジェクトを定義するそうです。

DESIGNとかTOP とかなんのこっちゃか意味がわかりませんが、とりあえずこう書いておけばいいみたいです。

BOARD には使用するボード定義名を記載します。これは一回普通に Vivado でプロジェクトを作成してみて、自分が作りたいボードの定義名をProject Summary とかからコピーするのが一番です(↓)。

BOARD_REPO は私が Vivado に定義されてない変なボードを使ってるから必要になるだけで通常は不要です。

1.4 Vivado を開いて IP Integrator でせっちゃこ

再び shell に移動して、以下のコマンドを実行します。

これで、 Vivado のプロジェクトを作ってるれるそうです。

cmake .. make sample_design

すると、画面にコワイ謎文字列がいっぱい出てきてなんか終わります。

うまくいけば Vivado のプロジェクトが出来てるので、以下のコマンドで Vivado を開きます。

make open_sample_design

………ボタンがいっぱいあってコワイよぉ。

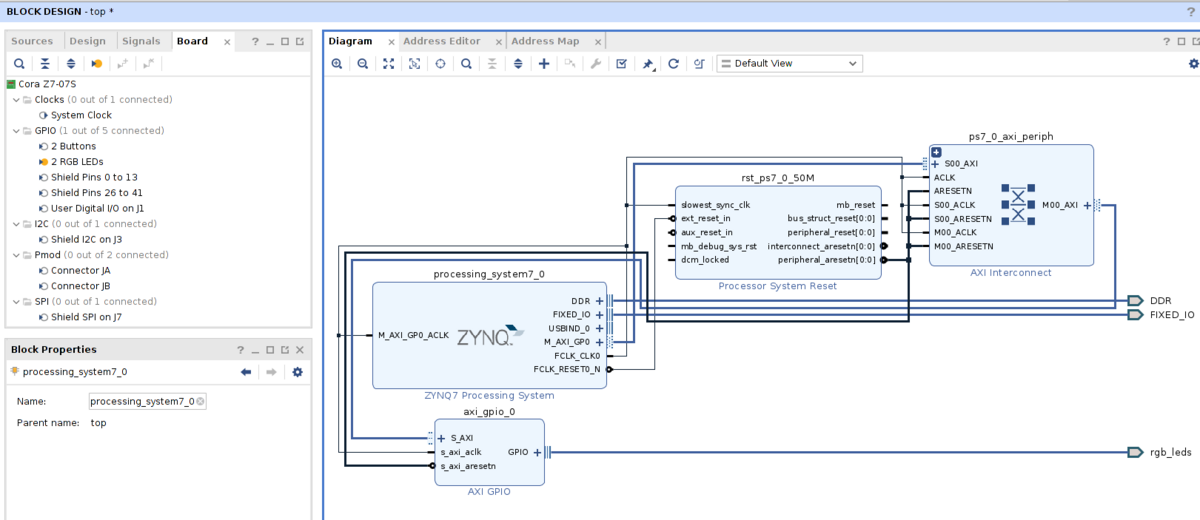

とりあえず、 IP Integrator の Open Block Design をクリックします。

後は Zync のProcessing Systemや Microblaze などを適当に配置して適当にAuto connect で接続します。

接続したら、この![]() ボタンを押して Validation チェックをします。

ボタンを押して Validation チェックをします。

成功したら Ctrl + S で Vivado を保存しましょう。まぁ、なんか Warningが出てますがよくわからんので無視します。

1.5 IP Integrator を出力する

ちゃんとVivado 保存しましたか?保存しましたね?Vivado 保存しましたね?

Vivado 保存したら、Vivado が保存されてることを確認して、再度Vivadoが保存されてることを確認してから、以下を実行します。

make export_bd_sample_design

すると、謎の top.tcl というコワイ ファイルが突然生成されます。

どうもこのコマンドを実行すると、作った IP Integrator の画面を復元するための謎ファイルを生成してくれるようです。

つまり、以下のような関係みたいですね。

では、本当に復元されるのか、Vivado をクローズし、一度全部削除してから試してみましょう。

なお、再三の忠告ですが、 Vivadoは保存してから makeコマンド実行しましたね?

make clear_sample_design make sample_design make open_sample_design

clear_sample_design はプロジェクトディレクトリごと全部削除してしまいますので、 Vivado を保存せずに export _bd_sample_design した場合はここで試合終了です。

ちゃんとVivado を保存してから、 export _bd_sample_design を実行した場合は、以下のようにIP Integrator が復元されます。

1.6 合成を試す

もし、合成を試したい場合は以下のコマンドで合成ができます。

make impl_sample_design

2. Vitis プロジェクトの作成とビルド

Vivado のデザインができたので、あとは Vitis でLチカプログラムを書くだけです。頑張りましょう。

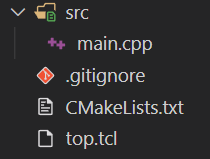

2.1 ソースファイル(src/main.cpp)を作成

まずは、 空の src/main.cpp を作成しておきます。

ディレクトリは src にしておくのが良いと思います。

2.2 Vitis プロジェクトを CMake に追加

CMakeLists.txt に以下を追加して、 Vitis プロジェクトを追加します。

add_vitis_hw_project( sample_app # プロジェクト名 XSA sample_design # Vivado プロジェクトを指定 PROC 知らんがな。馬鹿にすんな。 # 知らんがな SOURCES src # ソースコードディレクトリ )

………はぁ~………PROC とかまた頭おかしい知らんもんが出てくるし…。

ホンマ、人を馬鹿にされてるみたいで腹立つわぁ………。

いつになったらプログラムを書けるんだよ…。

何か知らんけど、 PROC というのは、搭載されてるプロセッサのことらしいです。

マジで知らんがな。人を馬鹿にすんなよ、オイ。私はプログラム書きたいだけだっつてんだろ、オォン!?

そこで、以下のコマンドを実行します。

make show_proc_sample_design

このコマンドでデザインに含まれるプロセッサを表示してくれます。

ただ、この時に一回 Vivado の合成が走るので結構時間がかかります。(謝罪:ハードウェアをエクスポートするだけなら合成は要らないという情報も見たのですが、一応合成してます)

しばらくすると、以下の様な文字列が表示されました。

----------------------------------------- Processors: /home/nodamushi/my_first_vitis_prj/build/sample_design.xsa ----------------------------------------- ps7_cortexa9_0 ----------------------------------------- [100%] Built target show_proc_sample_app

ps7_cortexa9_0 というのが搭載されてるプロセッサのようです。

なので、先ほどわからなくてイライラさせられたところは以下のようにします。

add vitis project · nodamushi/my_first_vitis_prj@83b5627 · GitHub

add_vitis_hw_project( sample_app # プロジェクト名 XSA sample_design # Vivado プロジェクトを指定 PROC ps7_cortexa9_0 # Processor SOURCES src # ソースコードディレクトリ )

以上で CMakeLists.txt は完成です。あとはプログラムを書いていくだけです。

2.3 Vitis プロジェクトを一度生成する

プログラムを書き始める前に、一度 Vitis のプロジェクトを作成します。

make create_sample_app

で、コマンドが完了したら、VS Code の「CMake: Delete Cache and Reconfigure」のコマンドを実行します。

よくわからないんですが、これを実行しないと、VS Code での補完が効かない様です。

2.4 Lチカプログラムを作成する

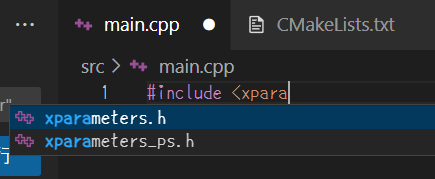

もう VSCode で補完が効くようになっているので、プログラムが書けます!

ほら、ちゃんと補完が効いてるよ!!

作ったコードはこちら。

2.5 ビルドをして実行

プログラムが完成したら、あとはビルドして書き込むだけです。

まずは、ビルドを行います。

make sample_app

これで、アプリケーションがビルドされます。

ビルドに成功したら、Vitis を起動して書き込みましょう。

make open_sample_app

上記のコマンドで Vitis が開きます。

残念なことに、なんかうっとうしい Welcom画面が開きます。×を押して閉じましょう。(これ開かないで済む方法あったら誰か教えてください)

×を押すと、上記のようにアプリケーションプロジェクトと、プラットフォームプロジェクトが表示されています。

既にビルドはされてるので、アプリケーションプロジェクトを右クリックして、Run As...からプログラムを書き込んで実行しましょう!

ひかったぞーいーーー

完!

注意事項:Vitis でファイルを追加した場合

注意事項として、新規にファイルを追加した場合は、一度 clear_sample_app を実行して削除してから、再度プロジェクトの作成から行う必要があります。

これは、 Vitis の💩仕様でフォルダをリンクしてるのではなく、コピーしているためです。

ファイルそのものはシンボリックリンク(ソフトリンク)させているので変更が反映されますが、フォルダの変更は反映されません。したがって、プロジェクトの作成からやり直す必要があります。

また、デバッグ中に Vitis 側でファイルを追加した場合なども、元のソースディレクトリには反映されません。手動でコピーしてください。

まとめ

最終的に作ったファイルはたったのこれだけです。

これだけなのに、6時間もかかってしまいました。

Vitis むつかしい………

ひとまず、本手順に従えば、 IP Integrator とか以外は基本的に GUI を触らなくていいので、初心者でもなんとかなると思います。